# Linear and Interface Circuit Applications

Volume 3

Data Acquisition, Peripheral Drivers and Hall-Effect Devices

D. E. Pippenger and E. J. Tobaben Linear Applications

Contributors

C. L. McCollum

Field Applications Engineering

Linear Product Engineering

European Edition

Revised and Edited by David P. E. Dale of the

European Linear Applications Staff

#### IMPORTANT NOTICE

Texas Instuments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

Texas Instruments assumes no responsibility for infringement of patents or rights of others based on Texas Instruments applications assistance or product specifications, since TI does not possess full access to data concerning the use or applications of customer's products. TI also assumes no responsibility for customer product designs.

Copyright © 1988 Texas Instruments

1st European Edition Vol 3

# Contents

|      | Title                        |                                          | Page         |

|------|------------------------------|------------------------------------------|--------------|

|      | Section 1 Data Acquis        |                                          |              |

| Data | Acquisition                  | ere statement i 🔻                        | 11-1         |

|      | INTRODUCTION                 | on production of the section of          | 11-1         |

|      | TYPICAL SYSTEMS              | enderske eielogske<br>merodon der (1866) | 11-1<br>11-4 |

|      | Data Logging                 |                                          | 11-5         |

|      | Process Control and Control  | Systems                                  | 11-5         |

|      | Communications               | ne talije ∰ dalektoke v                  | 11-5         |

|      | BASIC CONCEPTS               |                                          | 11-6         |

|      | Signals and Data Acquisition | Sampling Systems                         | 11-6         |

|      | Sampling Rate and Aliasing   |                                          | 11-6         |

|      | Continuous Time Signals and  | d Nyquist's Criterion                    | 11-6         |

|      | Ideal Sampled Frequency Sp   | ectrum                                   | 11-7         |

|      | Aliasing                     |                                          | 11-8         |

|      | Practical Constraints        |                                          | 11-9         |

|      | Sampling Transient Signals   | jan Aranja Aranja                        | 11-10        |

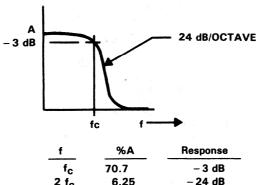

|      | Anti-Aliasing Filter         |                                          | 11-10        |

|      | Acquisition                  |                                          | 11-11        |

|      | A/D Conversion               |                                          | 11-12        |

|      | Quantisation                 |                                          | 11-12        |

|      | Quantisation Noise           |                                          | 11-14        |

|      | Encoding                     |                                          | 11-14        |

| Contents | LINEAR | AND |

|----------|--------|-----|

|          |        |     |

|   | Resolution                               | 11-14   |

|---|------------------------------------------|---------|

|   | Dynamic Range and Signal to Noise Ratio  | 11-14   |

|   | Signal Recovery                          | 11-15   |

|   |                                          |         |

|   |                                          |         |

| I | DATA ACQUISITION TERMINOLOGY             | 11-16   |

|   | Introduction                             | 11-16   |

|   | Nominal Midstep and Step Values          | 11 - 17 |

|   | Absolute Accuracy                        | 11-17   |

|   | Absolute Accuracy Error or Total Error   | 11-17   |

|   | Relative Accuracy Error                  | 11-17   |

|   | Quantisation Error                       | 11-18   |

|   | Code Width                               | 11-18   |

|   | Linearity Error or Integral Nonlinearity | 11-18   |

|   | Differential Nonlinearity                | 11-18   |

|   | Zero-Scale Error or Offset Error         | 11-20   |

|   | Full-Scale or Gain Error                 | 11-20   |

|   | Adjusted Error                           | 11-21   |

|   | Total Unadjusted Error                   | 11-21   |

|   | Monotonicity                             | 11-22   |

|   | Missing Codes                            | 11-22   |

|   | Acquisition Time                         | 11-22   |

|   | Aperture Time                            | 11-22   |

|   | Aperture Delay Time and Uncertainty      | 11-23   |

|   | Effective Aperture Delay Time            | 11-23   |

|   | Hold Time, Droop Rate                    | 11-23   |

|   | Settling Time                            | 11-23   |

|   | Access and Conversion Time               | 11-24   |

| INTERF | FACE APPLICATIONS                                      | Contents |

|--------|--------------------------------------------------------|----------|

|        | INPUT AND OUTPUT CODES                                 | 11-24    |

|        | Introduction                                           | 11-24    |

|        | Bipolar Codes                                          | 11-24    |

|        | Natural Binary                                         | 11-24    |

|        | Offset Binary                                          | 11-24    |

|        | One's and Two's Complement                             | 11-26    |

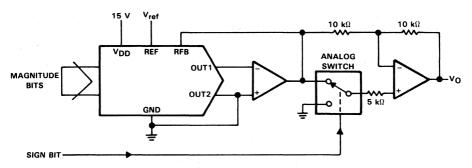

|        | Sign-Plus-Magnitude Code                               | 11-26    |

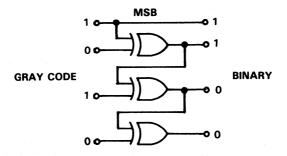

|        | Gray Code                                              | 11-27    |

|        | Binary-Coded-Decimal (BCD) Code                        | 11-29    |

|        | ANALOG-TO-DIGITAL CONVERSION TECHNIQUES                | 11-29    |

|        | Introduction                                           | 11-29    |

|        | Methods of Conversion                                  | 11-30    |

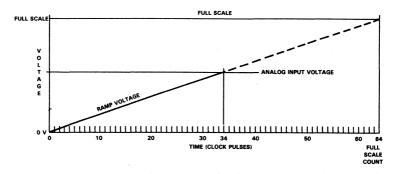

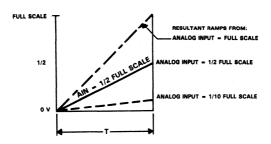

|        | Single-Slope A/D Converters                            | 11-30    |

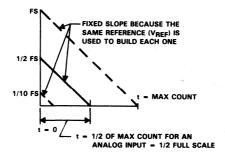

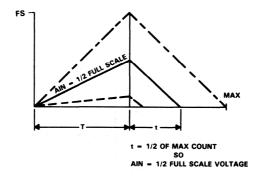

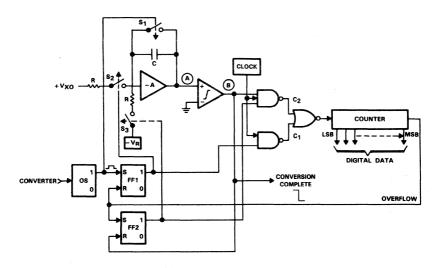

|        | Dual-Slope A/D Converters                              | 11-31    |

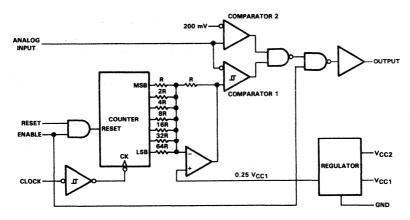

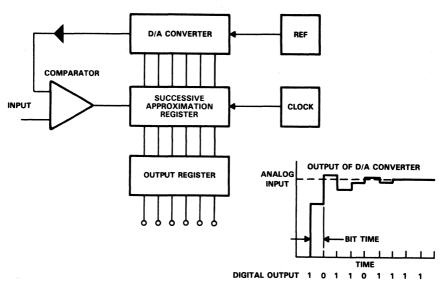

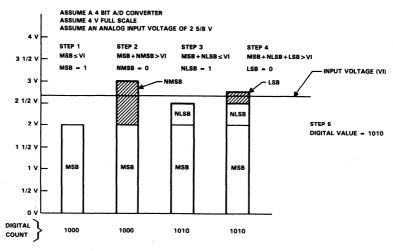

|        | Successive Approximation A/D Converters                | 11-33    |

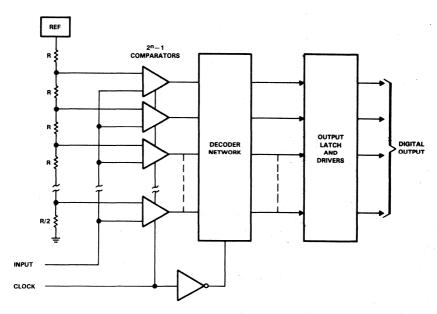

|        | Flash A/D Converters                                   | 11-35    |

|        | KEY SELECTION CRITERIA FOR DATA ACQUISITION COMPONENTS | 11-36    |

|        | DATA ACQUISITION DESIGN EXAMPLE                        | 11-38    |

|        | Introduction                                           | 11-38    |

|        | Example Specification                                  | 11-38    |

|        | Bits of Resolution                                     | 11-39    |

|        | Sampling Frequency – Determined from Alaising Error    | 11-40    |

|        | Recovery of Analog Output Signal                       | 11-42    |

|        | Stepped Output Error                                   | 11-42    |

|        | Sinx/x Error                                           | 11 – 44  |

| Aperture Error                                                               | 11-45   |

|------------------------------------------------------------------------------|---------|

| ANALOG-TO-DIGITAL AND DIGITAL-TO-<br>ANALOG CONVERTER DEVICES AND            |         |

| APPLICATIONS                                                                 | 11 - 47 |

| Introduction                                                                 | 11-47   |

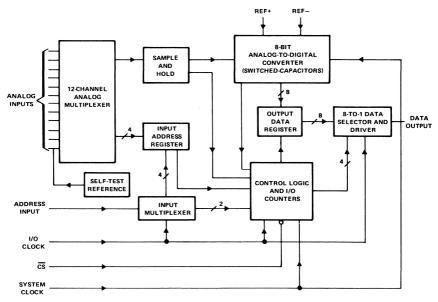

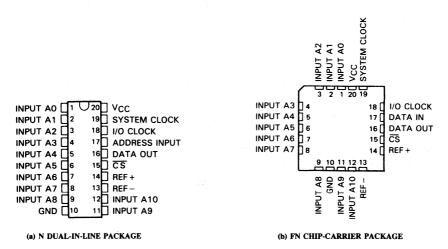

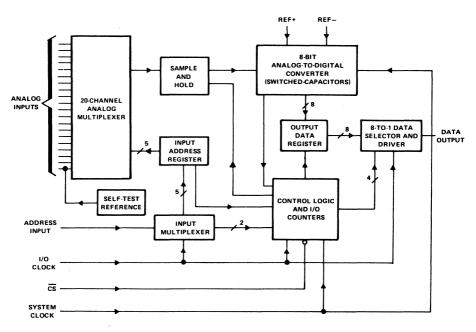

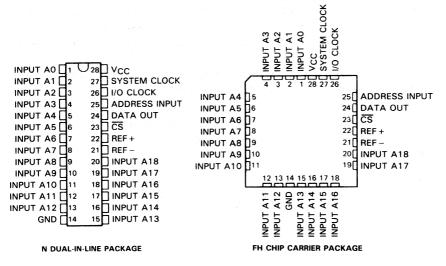

| TLC532A and TLC533A LinCMOS 8-Bit<br>ANALOG-TO-DIGITAL PERIPHERALS WITH      | 11 40   |

| PARALLEL INPUT/OUTPUT                                                        | 11-48   |

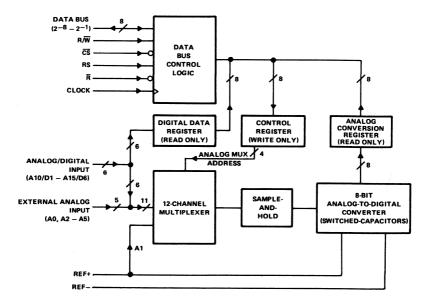

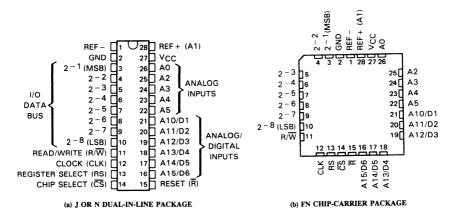

| Principles of Operation                                                      | 11-49   |

| TLC532A and TLC533A A/D Converter Interface to Zilog Z80A and Z80            |         |

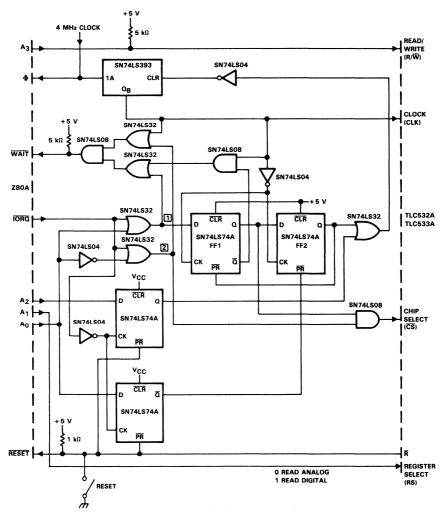

| Microprocessors                                                              | 11-53   |

| Input/Output Mapping                                                         | 11-55   |

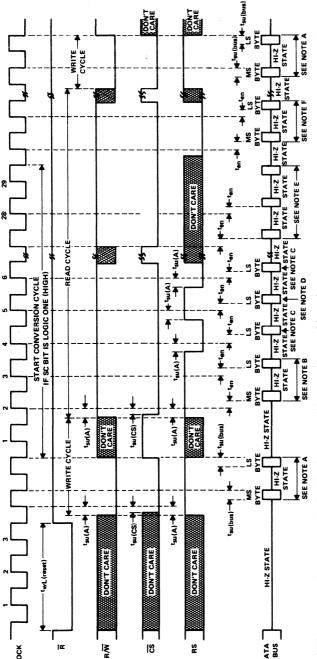

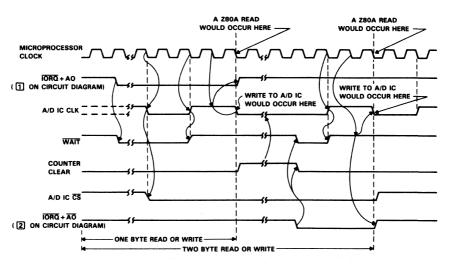

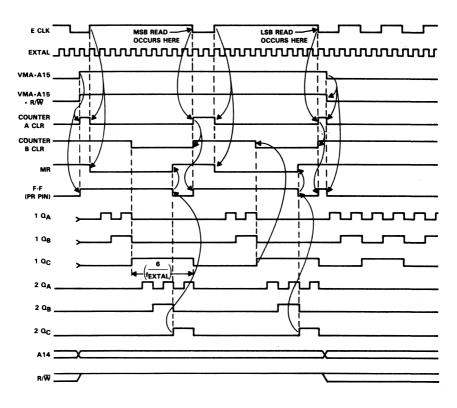

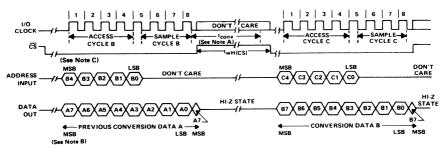

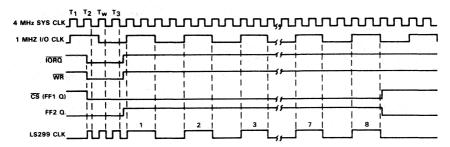

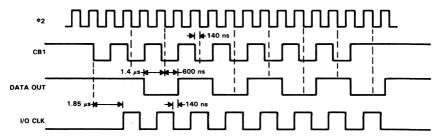

| Timing Diagram                                                               | 11 - 55 |

| Software                                                                     | 11 - 56 |

| Additional Comments                                                          | 11-57   |

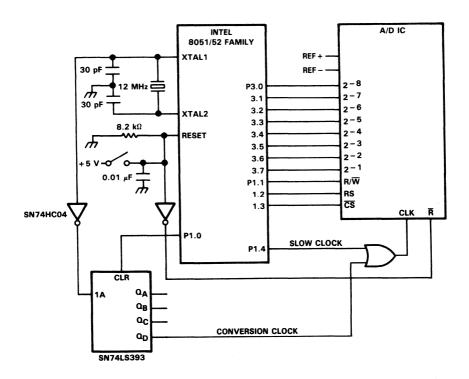

| TLC532A and TLC533A A/D Converter Interfacto Intel 8048, 8049, 8051 and 8052 | e       |

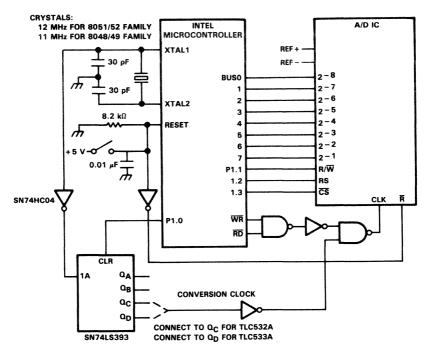

| Microcontrollers                                                             | 11 - 58 |

| Hardware-Interface 1                                                         | 11-58   |

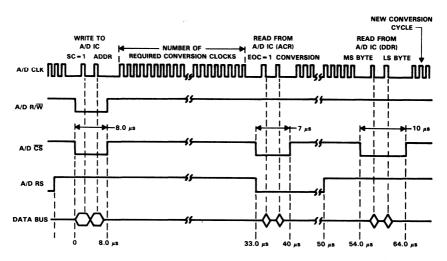

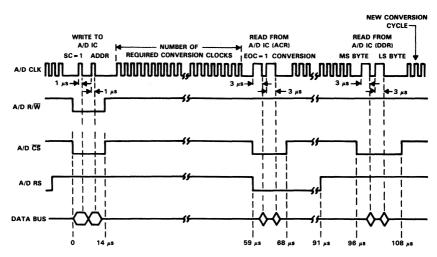

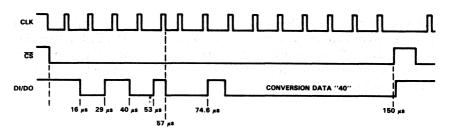

| Timing Diagram - Interface 1                                                 | 11-59   |

| Software - Interface 1                                                       | 11-61   |

| Hardware-Interface 2                                                         | 11-63   |

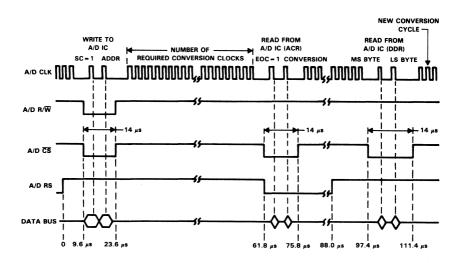

| Timing Diagram-Interface 2                                                   | 11-63   |

| Software – Interface 2                                                       | 11-64   |

| Additional Comments                                                          | 11-65   |

| TLC532A and TLC533A A/D Converter Interfac                                   | e       |

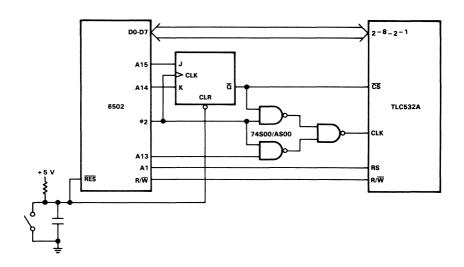

| to Rockwell 6502 Microprocessors                                             | 11-66   |

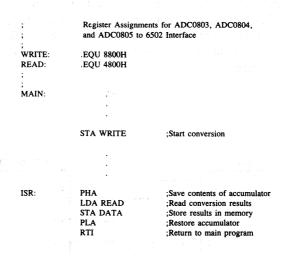

| Principals of Operation                                                      | 11-66   |

| INTERF | ACE APPLICATIONS                                                                                         | Contents |

|--------|----------------------------------------------------------------------------------------------------------|----------|

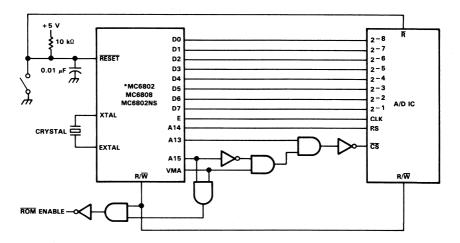

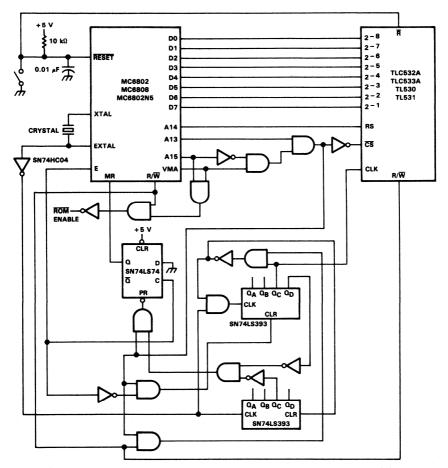

|        | TLC532A and TLC533A A/D Converter<br>Interface to Motorola 6800, 6802, 6809 and<br>6809E Microprocessors | 11-68    |

|        | Input/Output Mapping                                                                                     | 11-70    |

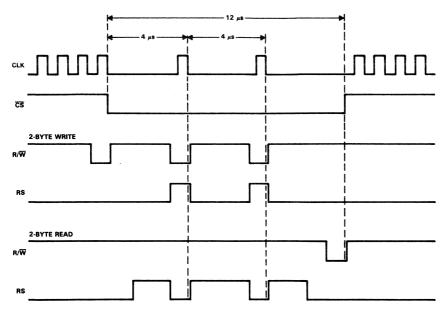

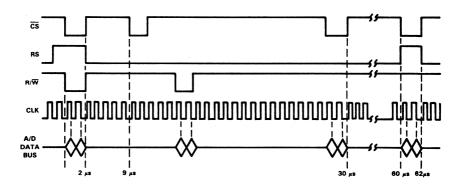

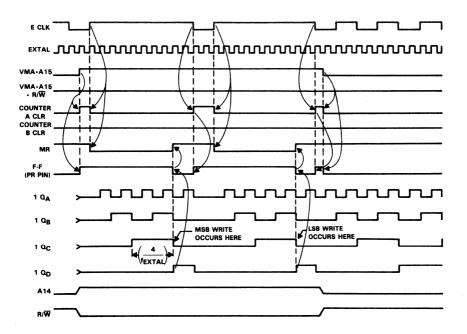

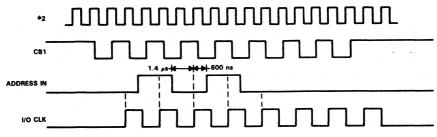

|        | Timing Diagram                                                                                           | 11-70    |

|        | Software                                                                                                 | 11-72    |

|        | Considerations for Different Microprocessors                                                             | 11-73    |

|        | Interface Selection                                                                                      | 11 - 74  |

|        | Additional Comments                                                                                      | 11-74    |

|        | TLC540 SERIES OF 8-BIT ANALOG-TO-<br>DIGITAL PERIPHERALS WITH SERIAL<br>INPUT/OUTPUT                     | 11-76    |

|        | TLC540 and TLC541 8-Bit Analog to Digital<br>Converters with 11-Inputs and Serial<br>Input/Output        | 11-76    |

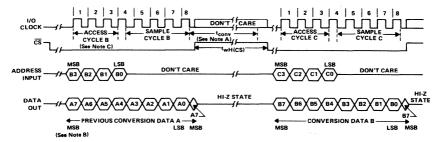

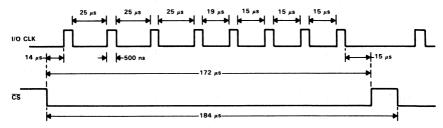

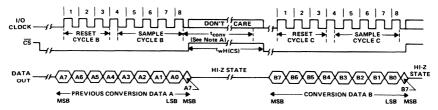

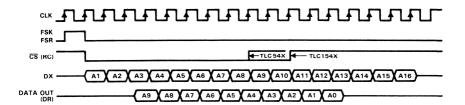

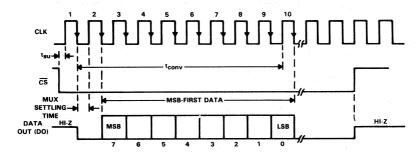

|        | TLC540, TLC541 Operation                                                                                 | 11-77    |

|        | Control Sequence                                                                                         | 11-79    |

|        | Sample and Hold Control                                                                                  | 11 - 80  |

|        | Combined System and I/O Clock Operation                                                                  | 11-80    |

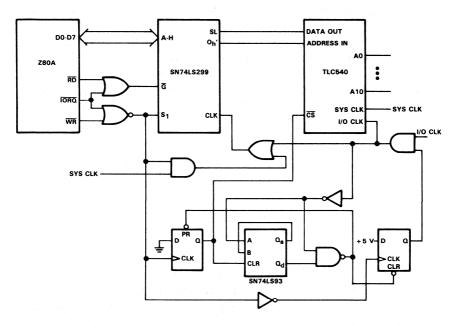

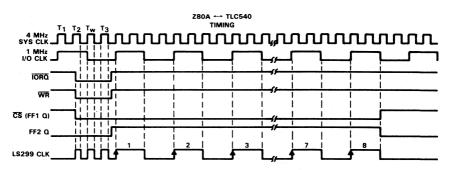

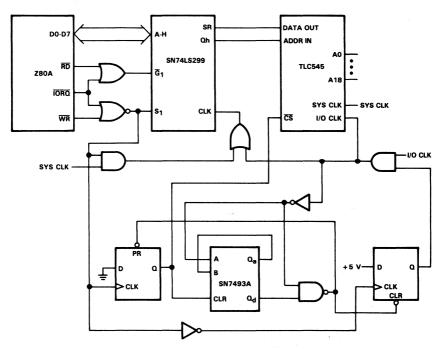

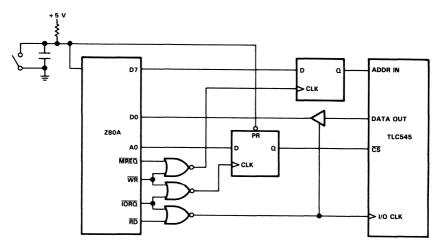

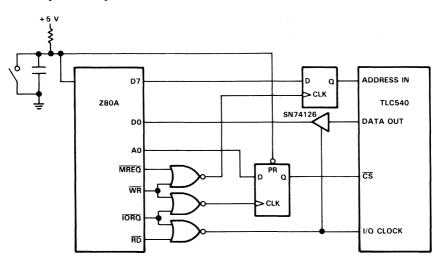

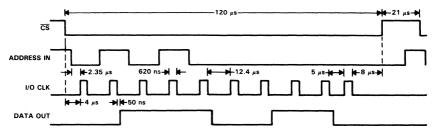

|        | TLC540 A/D Converter Interface to Zilog Z80A and Z80 Microprocessors                                     | 11-81    |

|        | Interface 1                                                                                              | 11-81    |

|        | Interface 2                                                                                              | 11-83    |

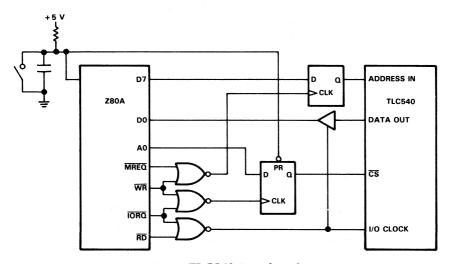

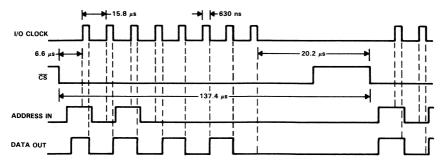

|        | TLC540 A/D Converter Interface to Rockwell 6502 Microprocessors using the                                | 44 0-    |

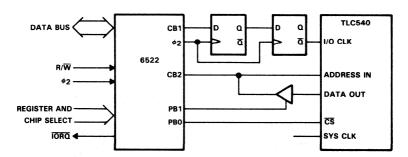

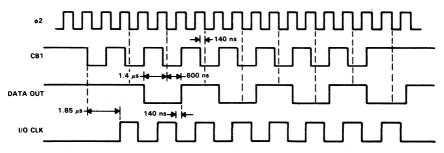

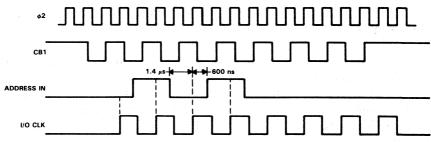

|        | 6522 VIA                                                                                                 | 11-85    |

|        | Principles of Operation                                                                                  | 11-85    |

|        | TLC540 A/D Converter Interface to                                                                        |          |

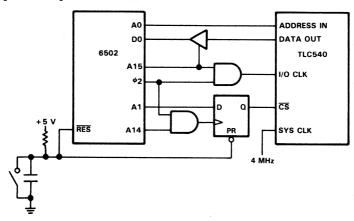

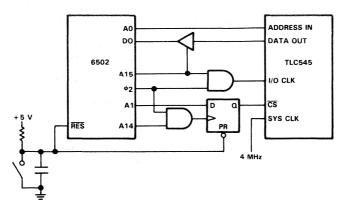

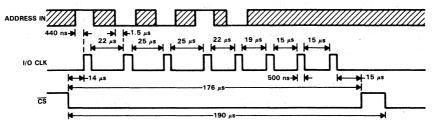

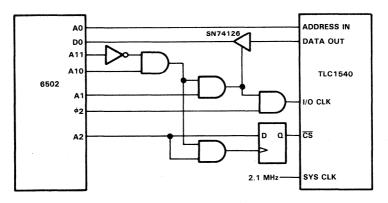

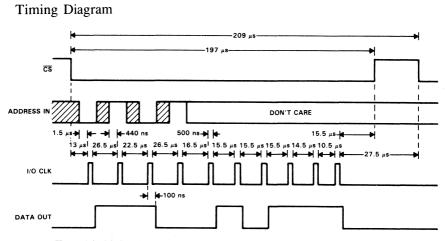

Rockwell 6502 Microprocessors using TTL Gates 11-87

11 - 87

Principles of Operation

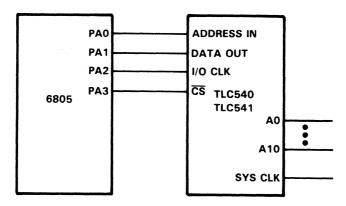

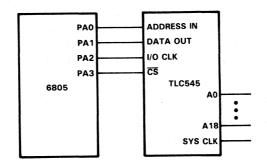

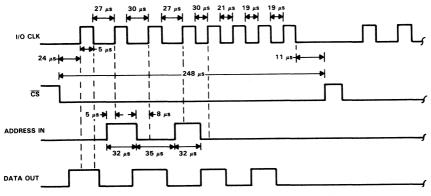

| TLC540 and TLC541 A/D Converter Interface Motorola 6805 Microcomputers                                | to<br>11-89 |

|-------------------------------------------------------------------------------------------------------|-------------|

| Principles of Operation                                                                               | 11-89       |

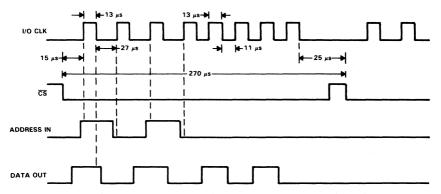

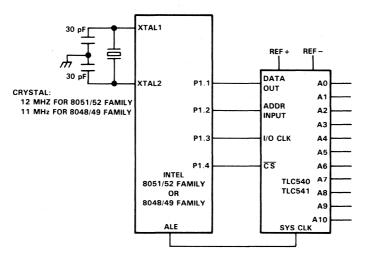

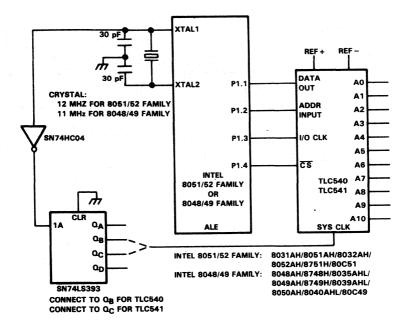

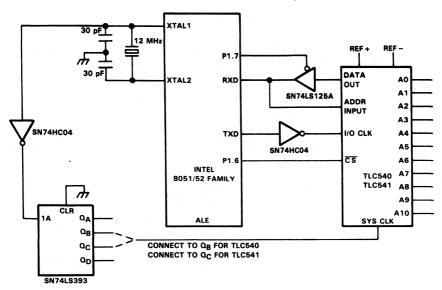

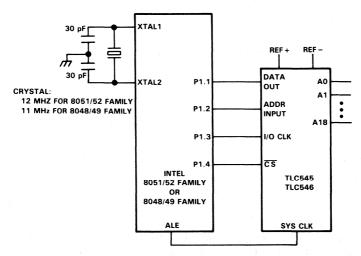

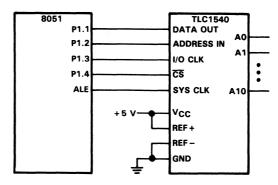

| TLC540 and TLC541 A/D Converter Interface<br>to Intel 8051 and 8052 Microcontroller Parallel<br>Ports | 11-91       |

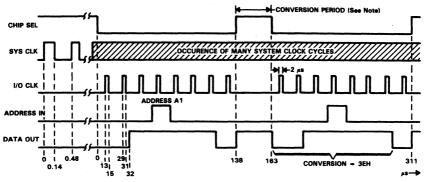

| Interface 1 (ALE CLOCK)                                                                               | 11-92       |

| Interface 2 (CRYSTAL CLOCK)                                                                           | 11-92       |

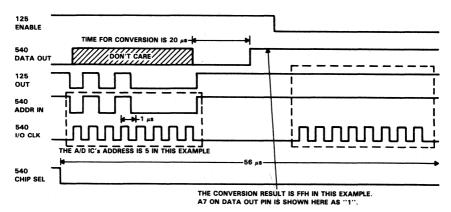

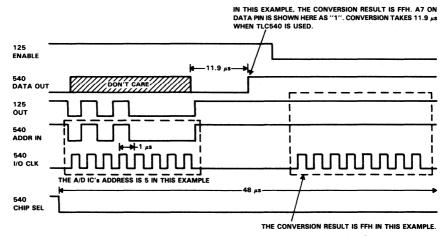

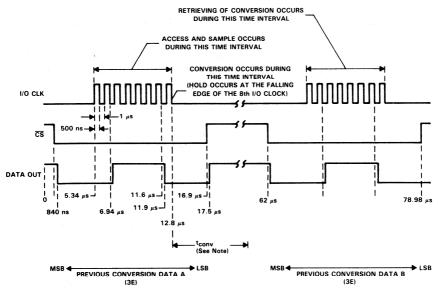

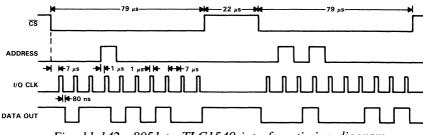

| Timing Diagrams                                                                                       | 11-92       |

| Software                                                                                              |             |

| Software                                                                                              | 11-94       |

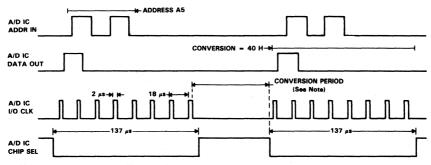

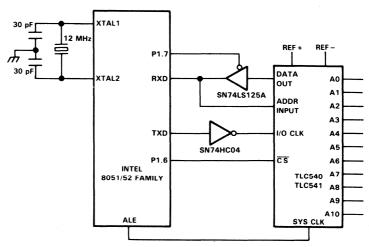

| TLC540 and TLC541 A/D Converter Interface to Intel 8051 and 8052 Microcontroller Serial               |             |

| Ports                                                                                                 | 11-96       |

| Timing Diagrams                                                                                       | 11-97       |

| Software                                                                                              | 11-98       |

| TLC540 and TLC541 A/D Converter Interface to Intel 8048 and 8049 Microcontroller Parallel             |             |

| Ports                                                                                                 | 11 - 100    |

| Hardware                                                                                              | 11 - 100    |

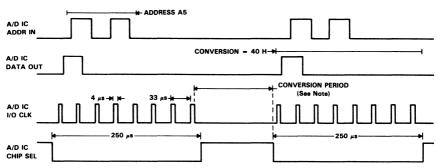

| Timing Diagrams                                                                                       | 11 - 100    |

| Software                                                                                              | 11 - 100    |

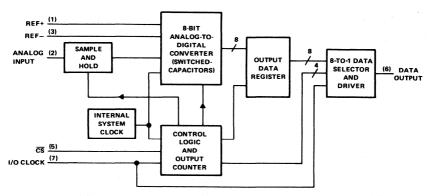

| TLC545 and TLC546 8-Bit Analog to Digital<br>Converters with 19-Inputs and Serial                     |             |

| Input/Ouptut                                                                                          | 11 - 102    |

| TLC545, TLC546 Operation                                                                              | 11 - 103    |

| TLC545 and TLC546 A/D Converter Interface to Zilog Z80A Microprocessors Using                         | 11 101      |

| Hardware Control                                                                                      | 11-104      |

| TLC545 A/D Converter Interface to<br>Zilog Z80A Microprocessors Using Software<br>Control             | 11 – 106    |

| V 40000 F 400                                                                                         | 11-1106     |

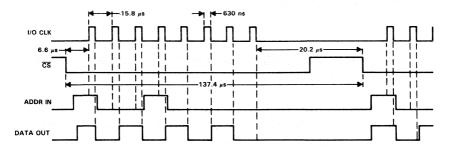

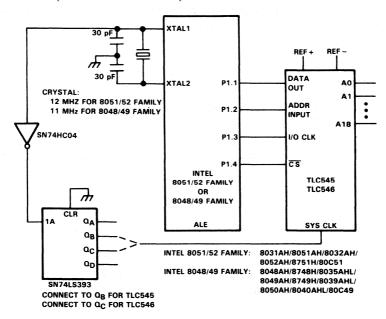

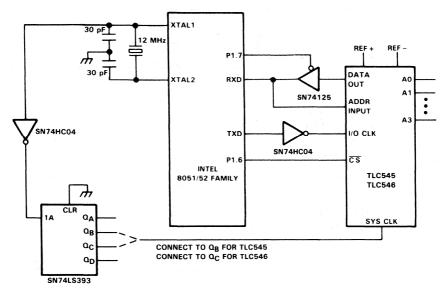

| TLC545 and TLC546 A/D Converter Interface to Intel 8051 and 8052 Microcontroller Parallel                         |                      |

|-------------------------------------------------------------------------------------------------------------------|----------------------|

| Ports                                                                                                             | 11 - 108             |

| Interface 1 (ALE CLOCK)                                                                                           | 11 - 108             |

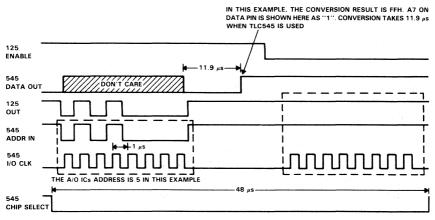

| Interface 2 (CRYSTAL CLOCK)                                                                                       | 11 - 108             |

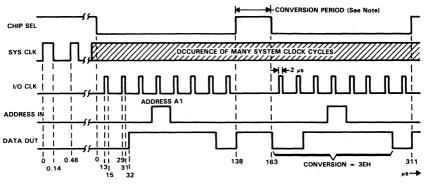

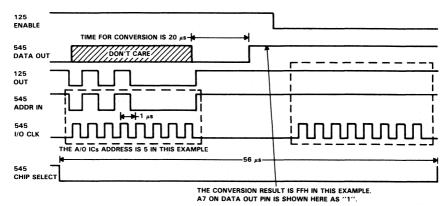

| Timing Diagrams                                                                                                   | 11 - 110             |

| Software                                                                                                          | 11-111               |

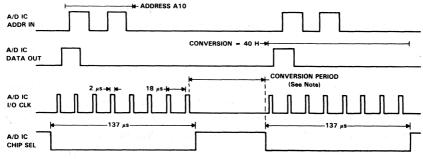

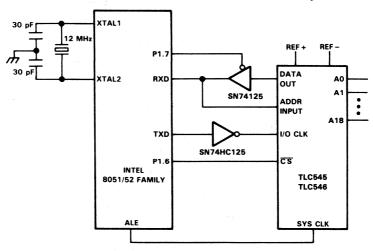

| TLC545 and TLC546 A/D Converter Interface t<br>Intel 8051 and 8052 Microcontroller Serial Ports                   |                      |

| Hardware                                                                                                          | 11-113               |

| Timing Diagrams                                                                                                   | 11-113               |

| Software                                                                                                          | 11-114               |

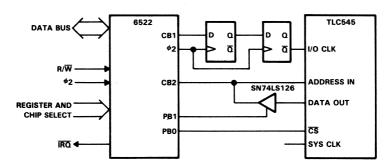

| TLC545 A/D Converter Interface to<br>Rockwell 6502 Microprocessors using the<br>6522 VIA  Principles of Operation | 11-116<br>11-116     |

| TLC545 A/D Converter Interface to<br>Rockwell 6502 Microprocessors using TTL Gate                                 | s 11–118             |

| Principles of Operation                                                                                           | 11-119               |

| TLC545 and TLC546 A/D Converter Interface of Motorola 6805 Microcomputers                                         | t <b>o</b><br>11–121 |

| Principles of Operation                                                                                           | 11-121               |

| TLC548 and TLC549 8-Bit Analog-to-Digital Converters with Serial Output                                           | 11-123               |

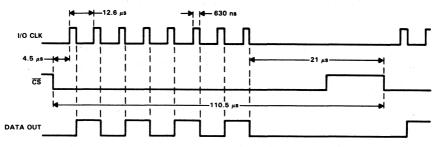

| Control Sequence                                                                                                  | 11-124               |

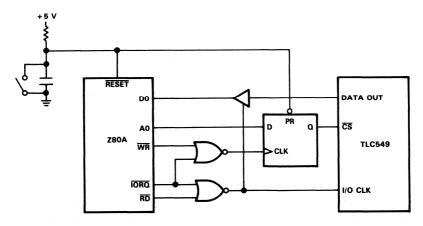

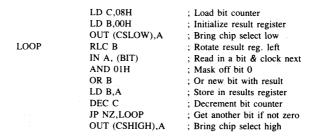

| TLC549 A/D Converter Interface to Zilog Z80A Microprocessors                                                      | 11 – 125             |

| Principles of Operation                                                                                           | 11 - 123             |

| - imelpies of operation                                                                                           | 11 14/               |

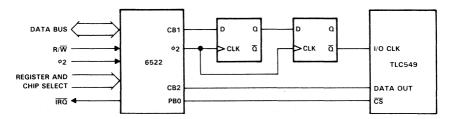

| TLC549 A/D Converter Interface to<br>Rockwell 6502 Microprocessors using the<br>6522 VIA    | 11 127   |

|---------------------------------------------------------------------------------------------|----------|

|                                                                                             | 11-127   |

| Principles of Operation                                                                     | 11-127   |

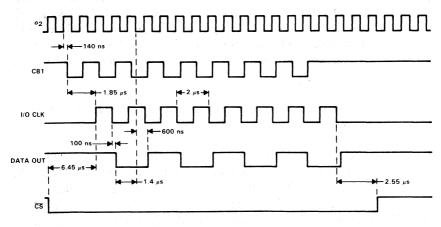

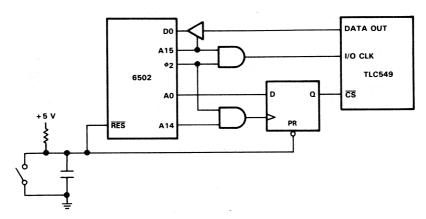

| TLC549 A/D Converter Interface to<br>Rockwell 6502 Microprocessors using TTL Gates          | 11-128   |

| Principles of Operation                                                                     | 11-129   |

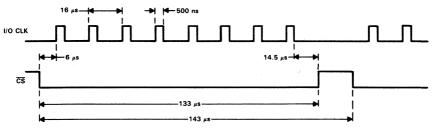

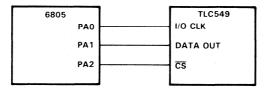

| TLC549 A/D Converter Interface to<br>Motorola 6805 Microcomputers                           | 11-130   |

| Principles of Operation                                                                     | 11-130   |

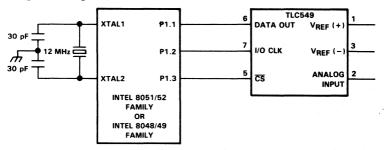

| TLC549 A/D Converter Interface to<br>Intel 8048 and 8049 Microcontroller Parallel<br>Ports  | 11-132   |

| Principles of Operation                                                                     | 11-132   |

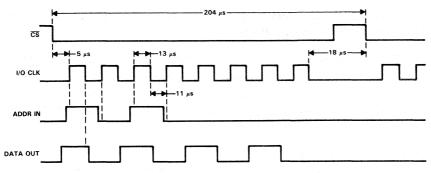

| Timing Diagram                                                                              | 11-132   |

| Software                                                                                    | 11-133   |

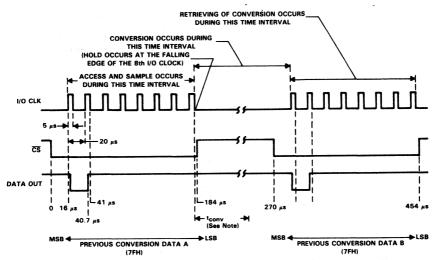

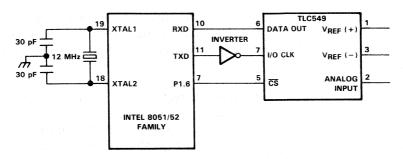

| TLC549 A/D Converter Interface to Intel 8051 and 8052 Microcontroller Serial Ports          | 11-134   |

| Principles of Operation                                                                     | 11-134   |

| Timing Diagram                                                                              | 11-135   |

| Software                                                                                    | 11-136   |

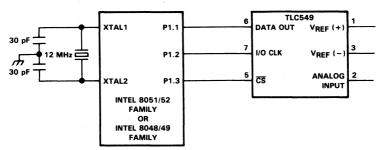

| TLC549 A/D Converter Interface to<br>Intel 8051 and 8052 Microcontroller Parallel<br>Ports  | 11-137   |

| Principles of Operation                                                                     | 11-137   |

| Timing Diagram                                                                              | 11-137   |

| Software                                                                                    |          |

|                                                                                             | 11-139   |

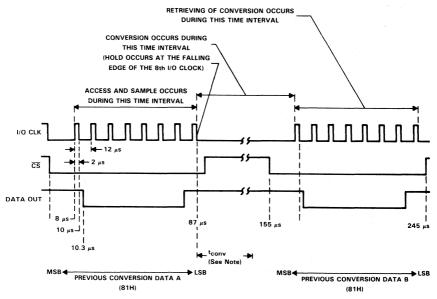

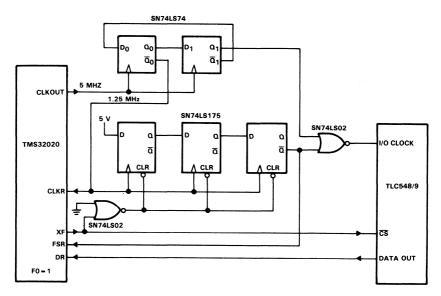

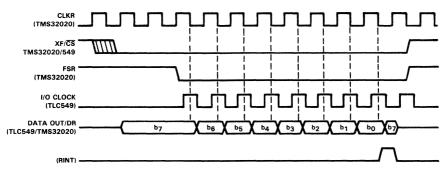

| TLC549 A/D Converter Interface to<br>Texas Instruments TMS32020 Digital Signal<br>Processor | 11 140   |

|                                                                                             | 11-140   |

| Hardware                                                                                    | 11-140   |

| Principles of Operation                                                                     | 11 - 141 |

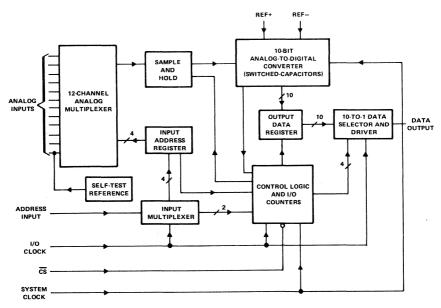

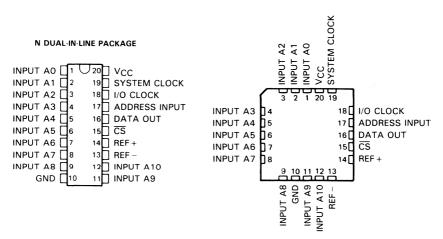

| TLC1540 and TLC1541 10-Bit Analog-to-Digital Converters with 11-Inputs and Serial Input/   |          |

|--------------------------------------------------------------------------------------------|----------|

| Output                                                                                     | 11-143   |

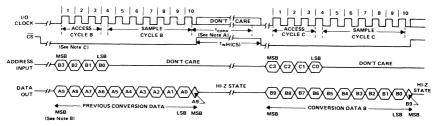

| TLC1540 and TLC1541 A/D Converter Interface                                                |          |

| to Zilog Z80A Microprocessors                                                              | 11 - 145 |

| Principles of Operation                                                                    | 11-145   |

| TLC1540 and TLC1541 A/D Converter Interface to Rockwell 6502 Microprocessors               | 11-147   |

| Hardware                                                                                   | 11-147   |

| Timing Diagram                                                                             | 11-148   |

| Software                                                                                   | 11-148   |

| TLC1540 and TLC1541 A/D Converter Interface                                                | <u>!</u> |

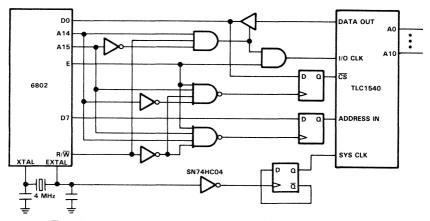

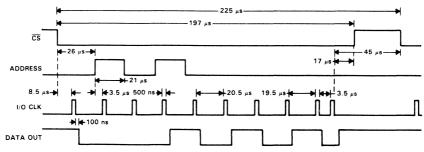

| to Motorola 6802 Microprocessors                                                           | 11-150   |

| Principles of Operation                                                                    | 11-150   |

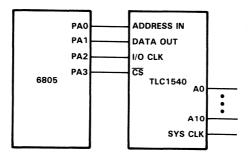

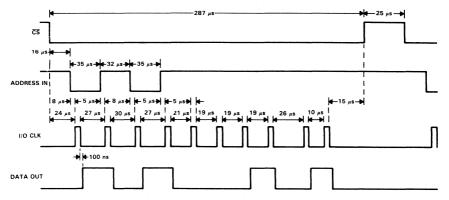

| TLC1540 and TC1541 A/D Converter Interface to Motorola 6805 Microcomputers                 | 11-152   |

| Hardware                                                                                   | 11-152   |

|                                                                                            | 11 - 152 |

| Software                                                                                   |          |

| TLC1540 amd TLC1541 A/D Converter Interfactor Intel 8051 and 8052 Microcontroller Parallel |          |

| Ports                                                                                      | 11-155   |

| Hardware                                                                                   | 11-155   |

| Timing Diagram                                                                             | 11-156   |

| Software                                                                                   | 11-156   |

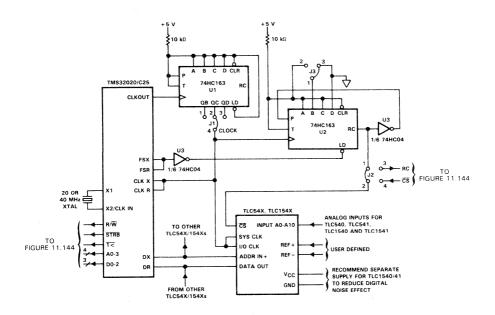

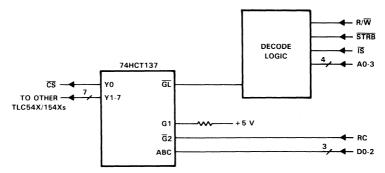

| TLC1540/1 and TLC540/1 A/D Converters<br>Interface to Texas Instruments TMS32020 and       |          |

| TMS32025 Digital Signal Processors                                                         | 11-158   |

| Hardware                                                                                   | 11-158   |

| Software                                                                                   | 11-160   |

| Other Considerations                                                                       | 11-162   |

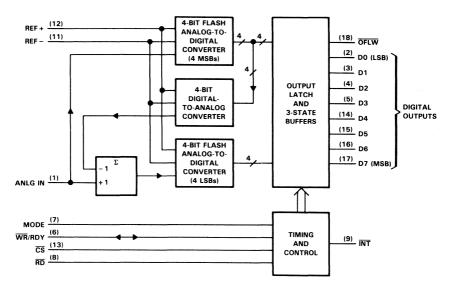

| TLC0820 ADVANCED LinCMOS HIGH-SPEED                                                                        |          |

|------------------------------------------------------------------------------------------------------------|----------|

| 8-BIT ANALOG-TO-DIGITAL CONVERTER                                                                          | 11 - 163 |

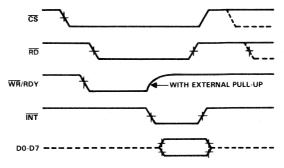

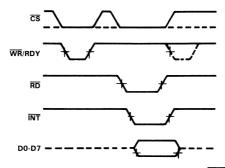

| Principles of Operation                                                                                    | 11-164   |

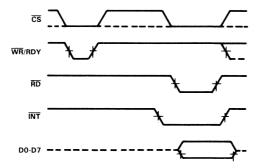

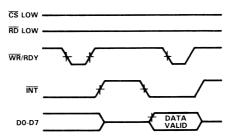

| Read Mode                                                                                                  | 11-164   |

| Write-Read Mode                                                                                            | 11-165   |

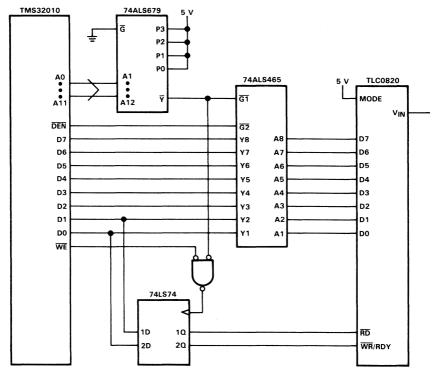

| TLC0820 A/D Converter Interface to<br>Texas Instruments TMS32010 Digital Signal<br>Processor               | 11-167   |

| Hardware                                                                                                   | 11-167   |

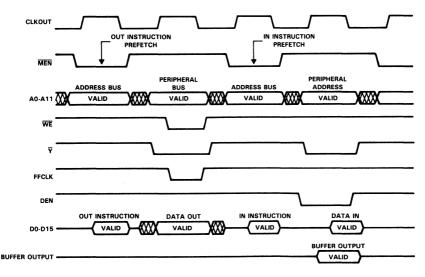

| Principles of Operation                                                                                    | 11 - 167 |

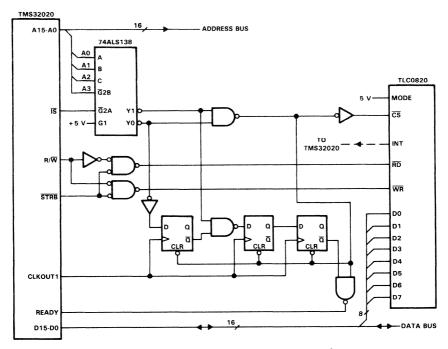

| TLC0820 A/D Converter Interface to Texas Instruments TMS32020 Digital Signal Processor                     | 11-107   |

| Hardware                                                                                                   | 11-170   |

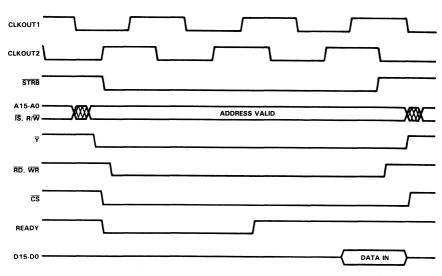

| Principles of Operation                                                                                    | 11-171   |

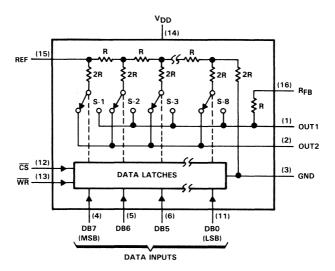

| TLC7524 ADVANCED LinCMOS 8-BIT<br>MULTIPLYING DIGITAL-TO-ANALOG<br>CONVERTER                               | 11-173   |

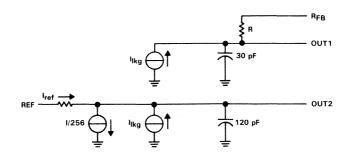

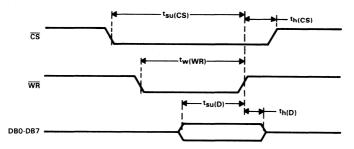

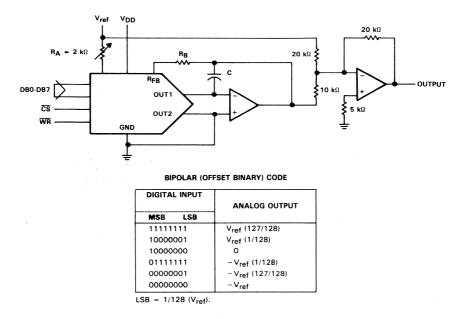

| Principles of Operation                                                                                    | 11-174   |

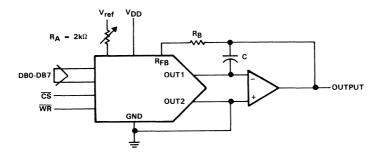

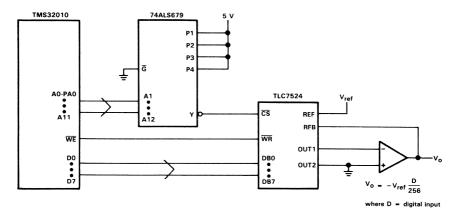

| TLC7524 Digital-to-Analog Converter Interface<br>to Texas Instruments TMS32010 Digital Signal<br>Processor | 11-177   |

| Hardware                                                                                                   | 11-177   |

| Principles of Operation                                                                                    | 11-177   |

| TLC7524 Digital-to-Analog Converter Interface<br>to Texas Instruments TMS32020 Digital Signal<br>Processor | 11-179   |

| Hardware                                                                                                   | 11-179   |

|                                                                                                            |          |

| Principles of Operation                                                                                    | 11-180   |

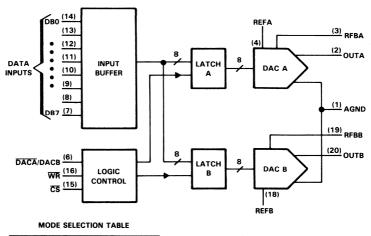

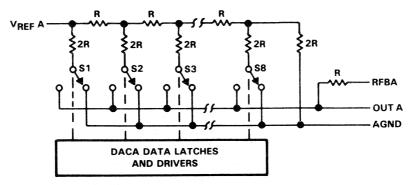

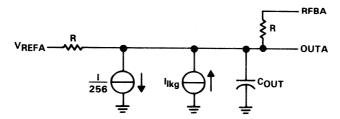

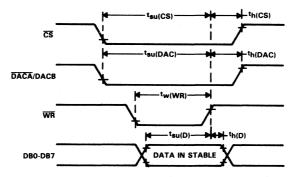

| TLC7528 ADVANCED LinCMOS DUAL 8-BIT<br>MULTIPLYING DIGITAL-TO-ANALOG<br>CONVERTER                          | 11 – 181 |

|                                                                                                            | 11-101   |

| TLC32040 FAMILY OF ANALOG INTERFACE CIRCUITS (AIC)                             | 11-187 |

|--------------------------------------------------------------------------------|--------|

| Introduction to Data Acquisition Devices for Digital Signal Processing         | 11-187 |

| TLC32040 AIC Interface to<br>TMS320 Family Digital Signal Processors           | 11-188 |

| Descripton                                                                     | 11-188 |

| Principles of Operation                                                        | 11-189 |

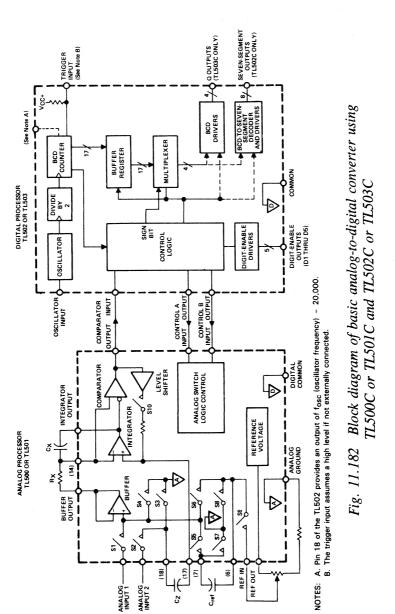

| TL500C THRO' TL503C DUAL-SLOPE-<br>INTEGRATING ANALOG-TO-DIGITAL<br>CONVERTERS | 11-193 |

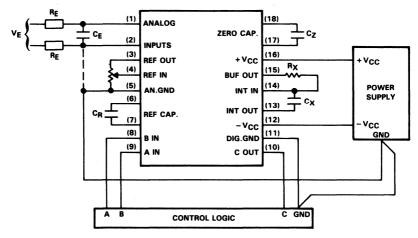

| General Overall Description                                                    | 11-194 |

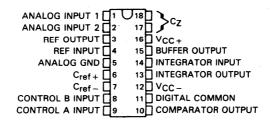

| Description of TL500C and TL501C Analog Processors                             | 11-196 |

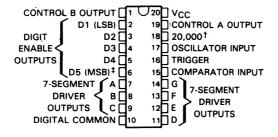

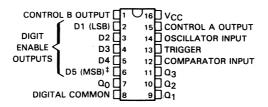

| Description of TL502C and TL503C Digital Processors                            | 11-197 |

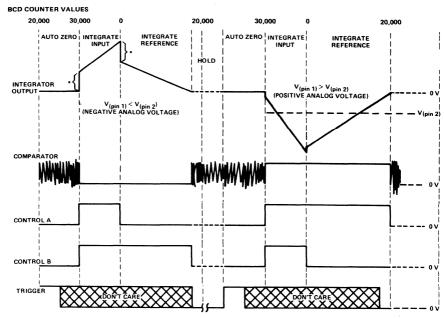

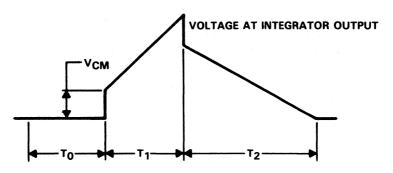

| Principles of Operation                                                        | 11-200 |

| Auto-Zero Phase                                                                | 11-201 |

| Integrate-Input Phase                                                          | 11-202 |

| Integrate-Reference Phase                                                      | 11-202 |

| TL500C Thru' TL503C Dual-Slope-Integrating A/D Application Examples            | 11-202 |

| External Component Selection Guide                                             | 11-204 |

| Printed Circuit Board Layout Notes                                             | 11-206 |

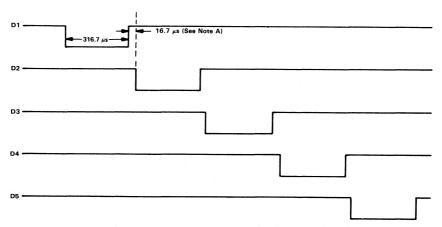

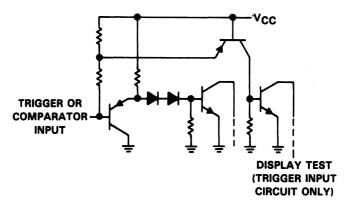

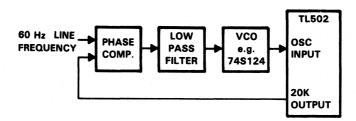

| TL502 and TL503 Control Circuits                                               | 11-207 |

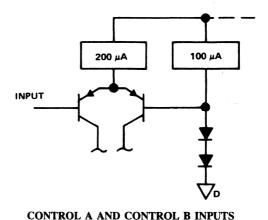

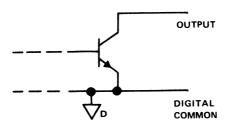

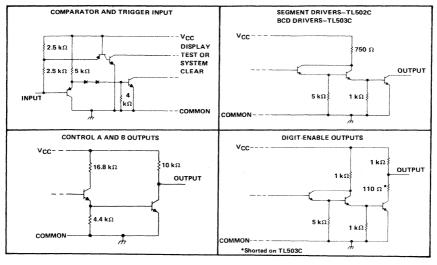

| Logic Inputs and Outputs                                                       | 11-208 |

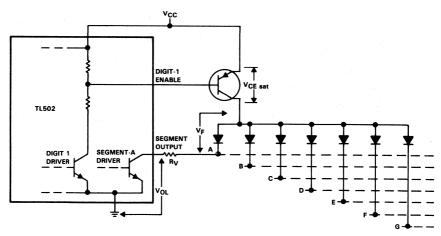

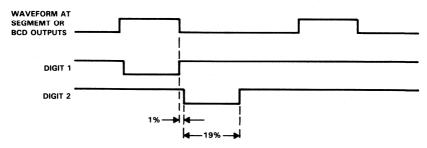

| Driving a Seven Segment Display Using TL502 Device                             | 11-209 |

| Calculation of Current Limiting Resistor                                       | 11-210 |

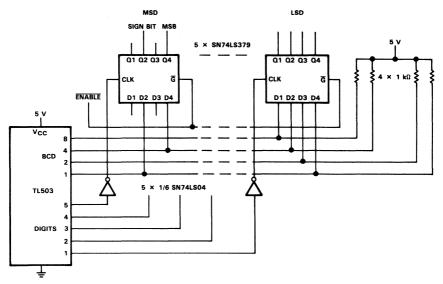

| Application of the TL503 BCD Outputs                                           | 11-211 |

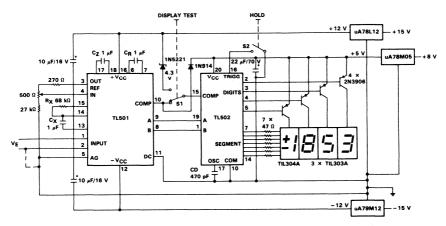

| Digital Panel Meter Using the TL501 and                                                    |          |

|--------------------------------------------------------------------------------------------|----------|

| TL502 Devices                                                                              | 11-212   |

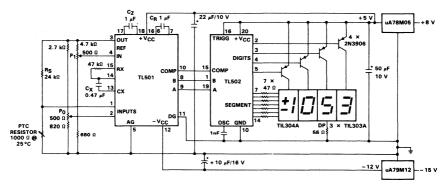

| Digital Thermometer                                                                        | 11-213   |

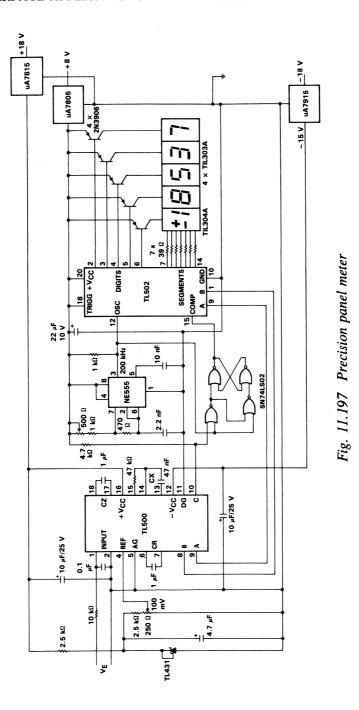

| Precision Panel Meter Application                                                          | 11 - 214 |

| TL507 SINGLE-SLOPE ANALOG-TO-DIGITAL                                                       |          |

| CONVERTER                                                                                  | 11-216   |

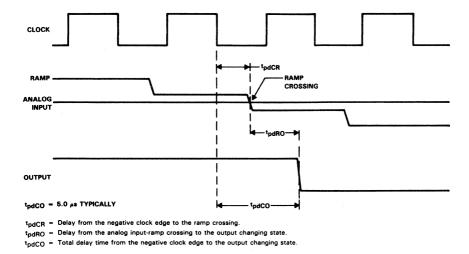

| Description                                                                                | 11 - 217 |

| Definition of Terms                                                                        | 11-217   |

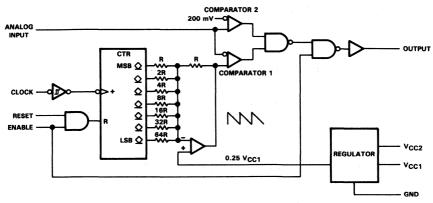

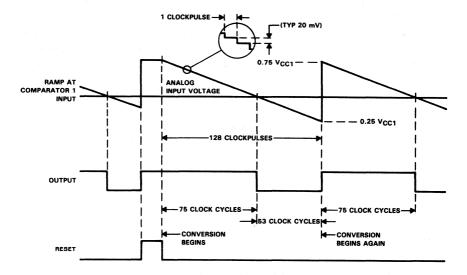

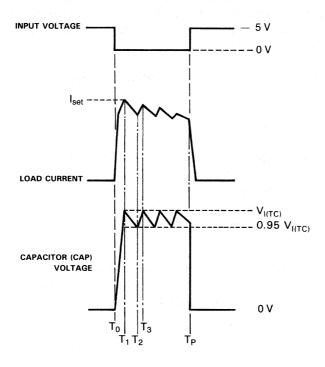

| Principles of Operation                                                                    | 11-218   |

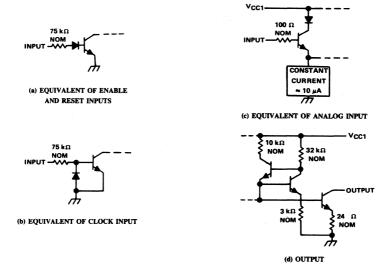

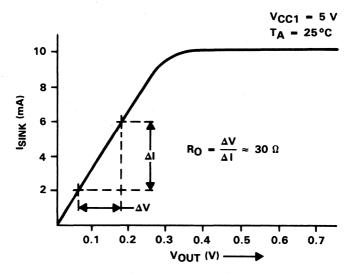

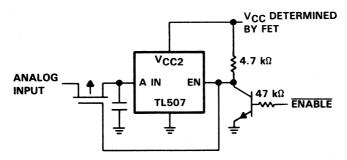

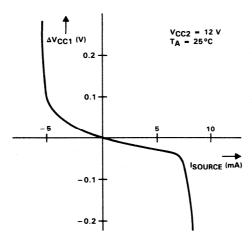

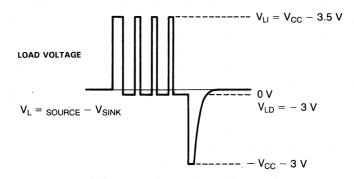

| TL507 Device Inputs and Outputs                                                            | 11-220   |

| TL507 Single-Slope Analog-to-Digital                                                       |          |

| Converter Applications                                                                     | 11 - 224 |

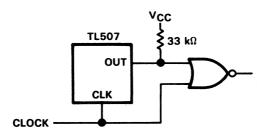

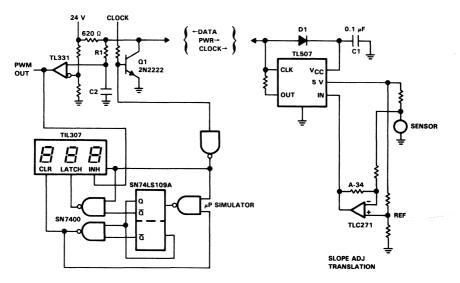

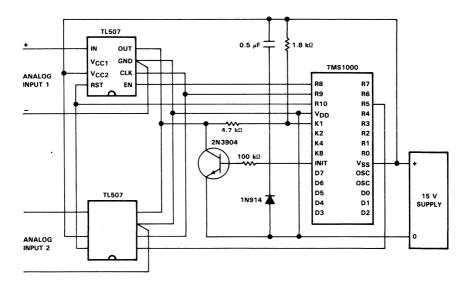

| Single-Wire, Power, Data and Clock Cycle Transmitter                                       | 11-224   |

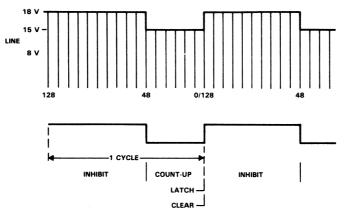

| TL507 High Voltage Isolation Application and                                               |          |

| Signal Coupling                                                                            | 11-225   |

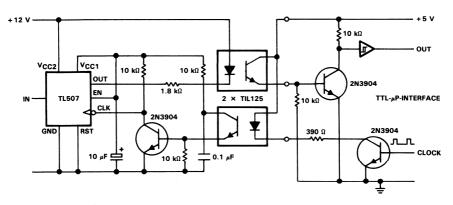

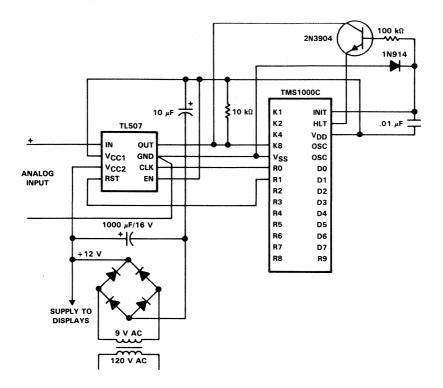

| TL507 to TMS1000 Interface                                                                 | 11-226   |

| TL507 to TMS1000C Interface                                                                | 11-227   |

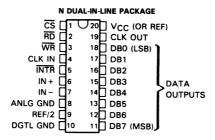

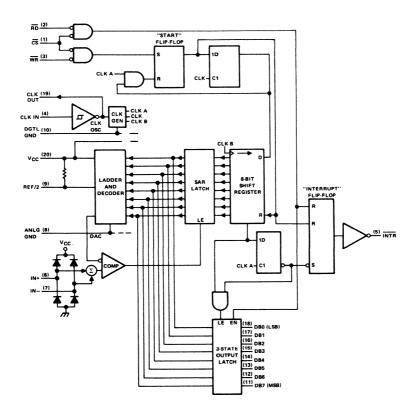

| ADC0803 AND ADC0805 8-BIT SUCCESSIVE APPROXIMATION A/D CONVERTERS WITH DIFFERENTIAL INPUTS | 11-228   |

| Description                                                                                | 11-228   |

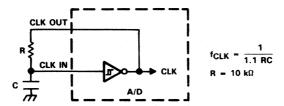

| Principles of Operation                                                                    | 11-229   |

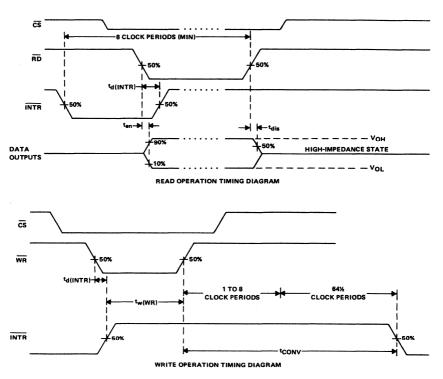

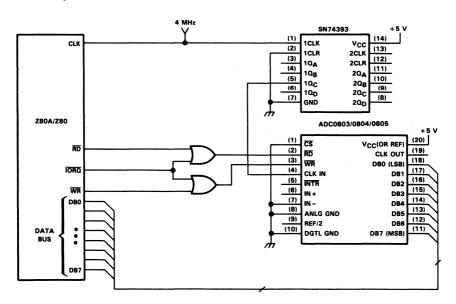

| ADC0803/4/5 A/D Converter Interface to Zilog Z80 and Z80A Microprocessors                  | 11-231   |

| Circuitry                                                                                  | 11-232   |

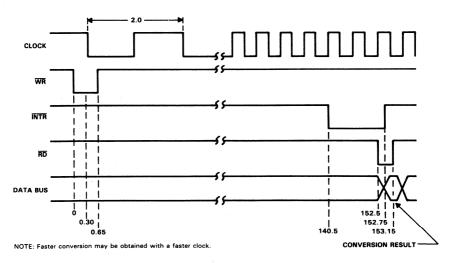

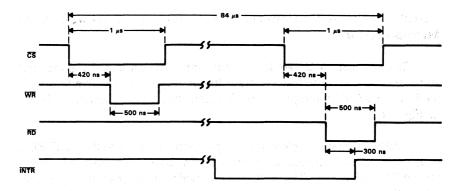

| Timing Diagram                                                                             | 11-233   |

| Software                                                                                   | 11-234   |

| ADC0803/4/5 A/D Converter Interface to                                                     |          |

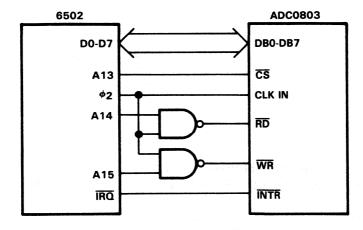

| Rockwell 6502 Microprocessors                                                              | 11-235   |

| ADC0808, ADC0809, TL0808 and TL0809 CMOS<br>8-BIT ANALOG-TO-DIGITAL CONVERTERS                               |          |

|--------------------------------------------------------------------------------------------------------------|----------|

| WITH 8-CHANNEL MULTIPLEXERS                                                                                  | 11 - 236 |

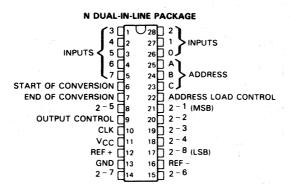

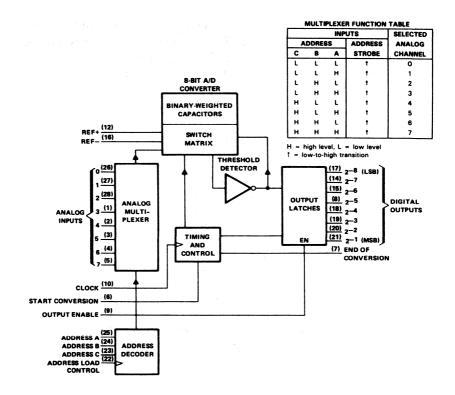

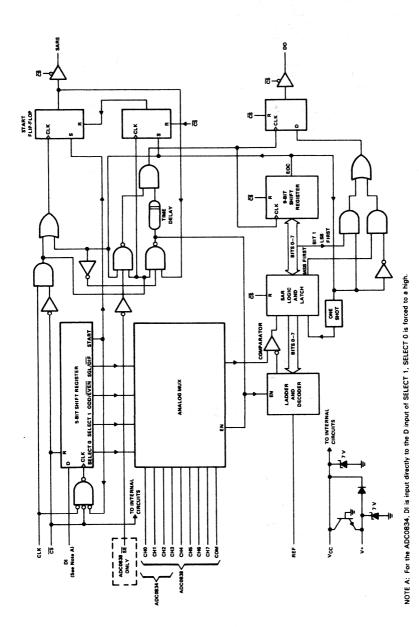

| Description                                                                                                  | 11-237   |

| Multiplexer                                                                                                  | 11-238   |

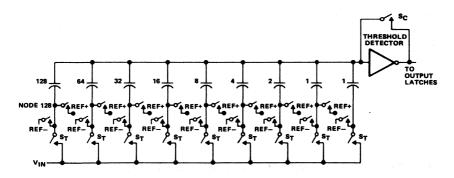

| Converter                                                                                                    | 11-239   |

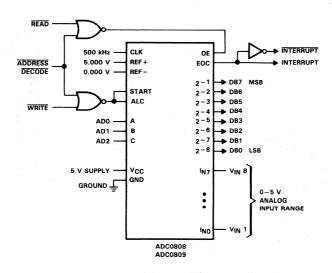

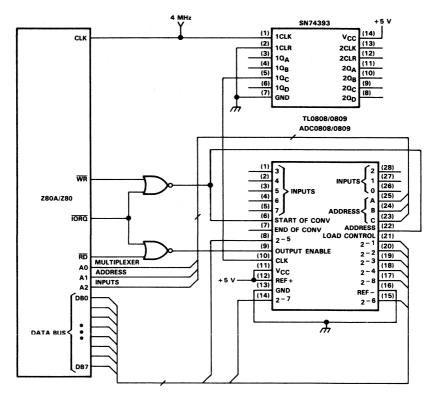

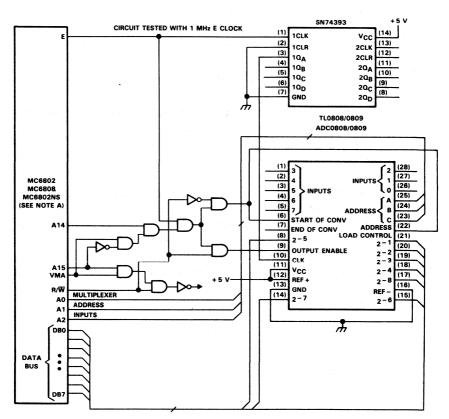

| ADC0808/9 and TL0808/9 A/D Converter<br>Interface to Zilog Z80A Microprocessors                              | 11-240   |

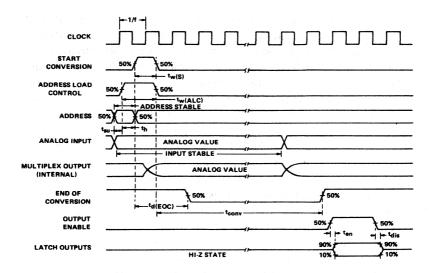

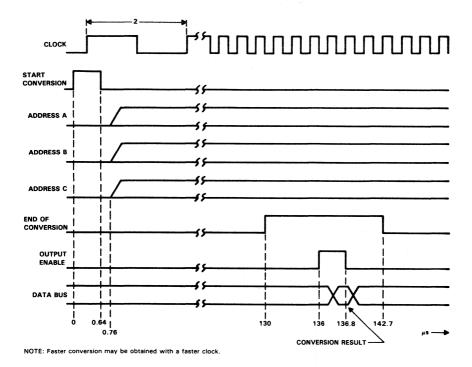

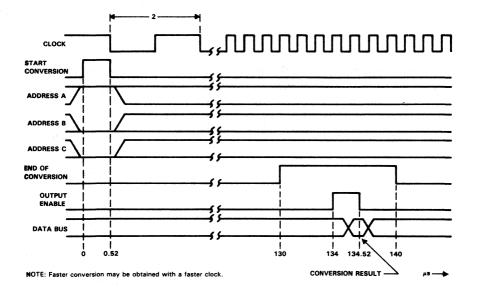

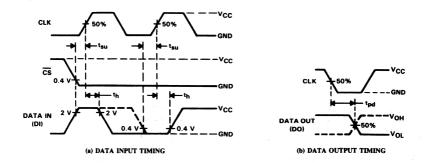

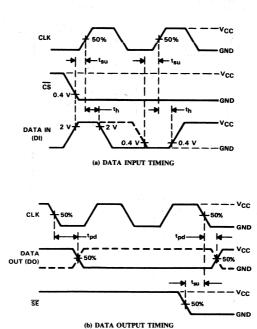

| Timing Diagram                                                                                               | 11-240   |

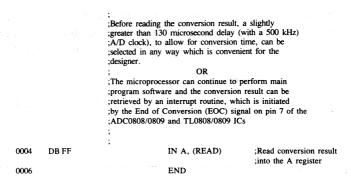

| Software                                                                                                     | 11-242   |

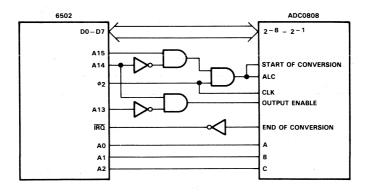

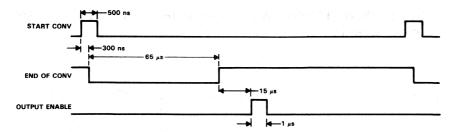

| ADC0808/9 and TL0808/9 A/D Converter Interfa                                                                 | ace      |

| to Rockwell 6502 Microprocessors                                                                             | 11-244   |

| ADC0808/9 and TL0808/9 A/D Converter                                                                         |          |

| Interface to Motorola 6800 Microprocessors                                                                   | 11 - 246 |

| Timing Diagram                                                                                               | 11 - 248 |

| Software                                                                                                     | 11-248   |

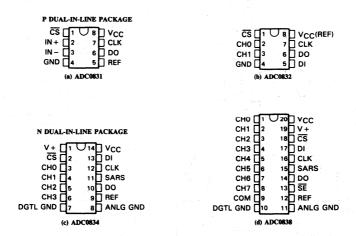

| ADC0831, ADC0832, ADC0834, ADC0838 8-BIT<br>A/D CONVERTERS WITH SINGLE<br>DIFFERENTIAL, 2, 4, 8-MULTIPLEXER, | 11 240   |

| CHANNEL OPTIONS AND SERIAL CONTROL                                                                           |          |

| Description                                                                                                  | 11-249   |

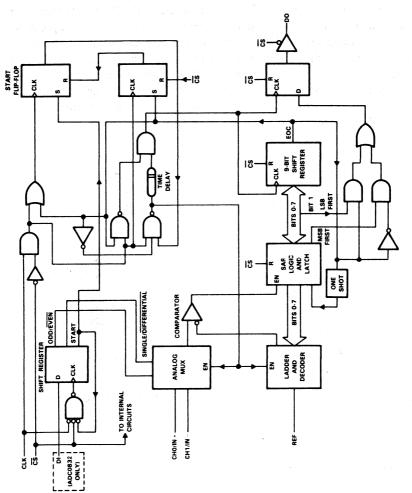

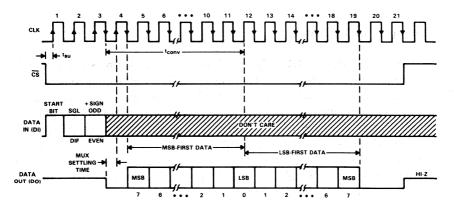

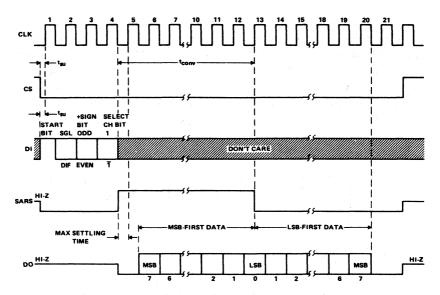

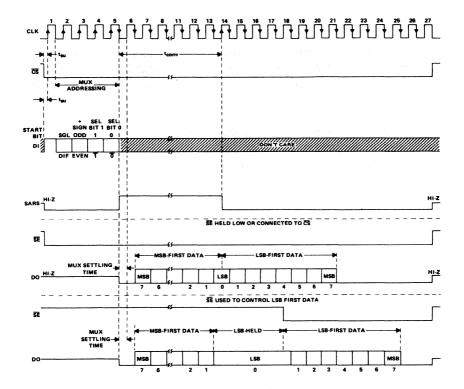

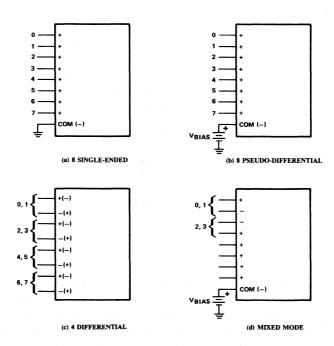

| Principles of Operation                                                                                      | 11-254   |

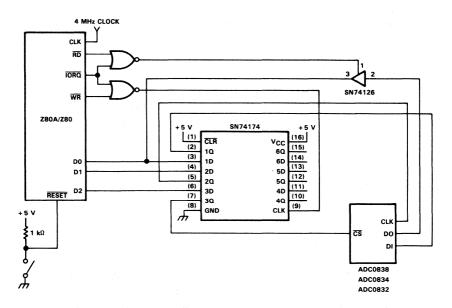

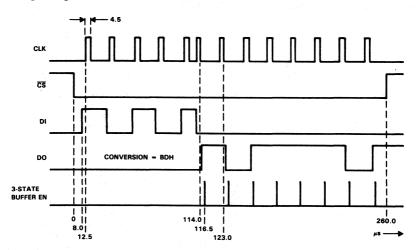

| ADC0831/0832/0834/0838 A/D Converter<br>Interface to Zilog Z80A and Z80<br>Microprocessors                   | 11-257   |

| •                                                                                                            | 11 257   |

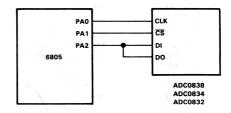

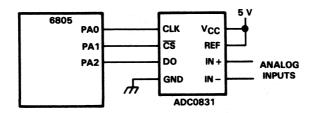

| Circuitry – ADC0832, ADC0834 and ADC0838 Devices                                                             | 11-258   |

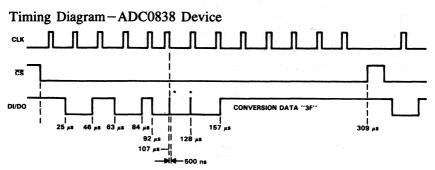

| Timing Diagram-ADC0838 Device                                                                                | 11-259   |

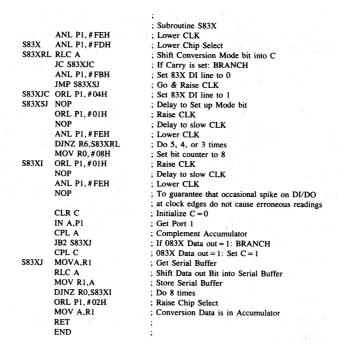

| Software – ADC0832, ADC0834 and ADC0838 Devices                                                              | 11-260   |

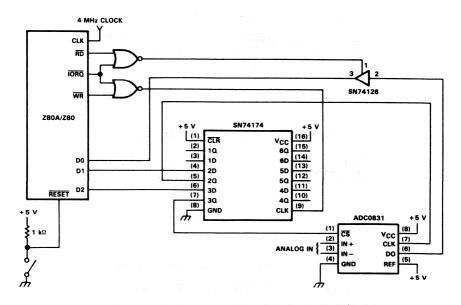

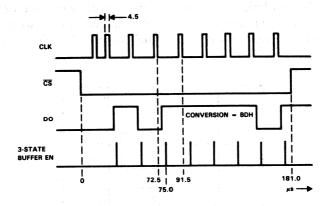

| Circuitry – ADC0831 Device                                                                                  | 11 - 262 |

|-------------------------------------------------------------------------------------------------------------|----------|

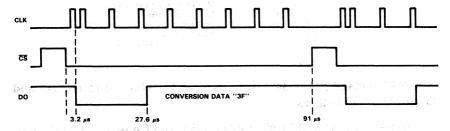

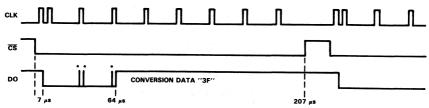

| Timing Diagram-ADC0831 Device                                                                               | 11-263   |

| Software - ADC0831 Device                                                                                   | 11-263   |

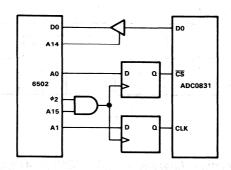

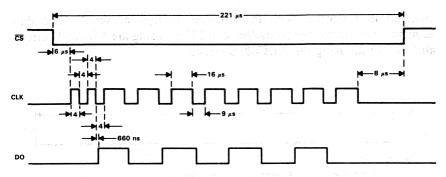

| ADC0831/0832/0838 A/D Converter Interface to Rockwell 6502 Microprocessors                                  | 11-264   |

| ADC0831/0832/0834/0838 A/D Converter<br>Interface to Motorola 6805 Microcomputers                           | 11-267   |

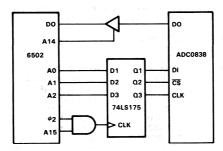

| Circuitry-ADC0832, ADC0834 and ADC0838 Devices                                                              | 11-268   |

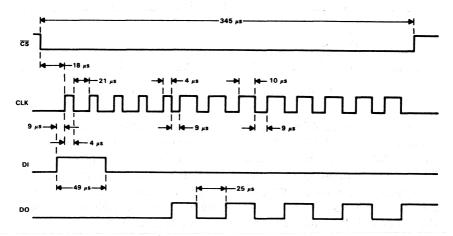

| Timing Diagram-ADC0838 Device                                                                               | 11-268   |

| Software – ADC0832, ADC0834 and ADC0838 Devices                                                             | 11-269   |

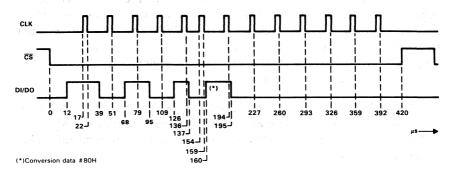

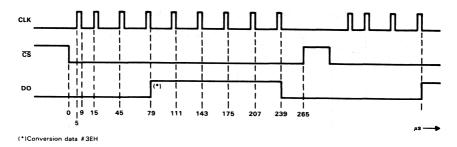

| Circuitry - ADC0831 Device                                                                                  | 11-271   |

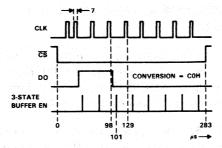

| Timing Diagram-ADC0831 Device                                                                               | 11-272   |

| Software - ADC0831 Device                                                                                   | 11-272   |

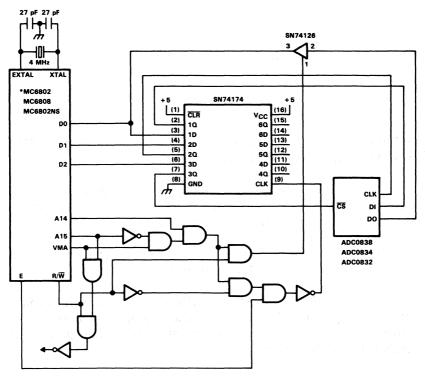

| ADC0831/0832/0834/0838 A/D Converter<br>Interface to Motorola 6800, 6802, 6809 and<br>6809E Microprocessors | 11-273   |

| Circuitry – ADC0832, ADC0834 and ADC0838 Devices                                                            | 11-273   |

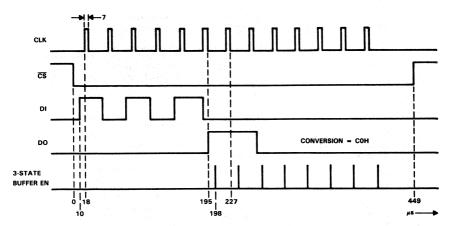

| Timing Diagram-ADC0838 Device                                                                               | 11-275   |

| Software – ADC0832, ADC0834 and ADC0838 Devices                                                             | 11-275   |

| Circuitry - ADC0831 Device                                                                                  | 11-278   |

| Timing Diagram-ADC0831 Device                                                                               | 11 - 278 |

| Software - ADC0831 Device                                                                                   | 11-279   |

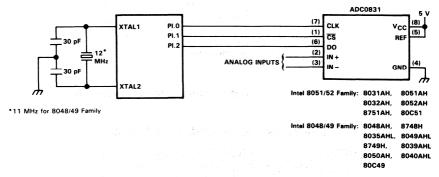

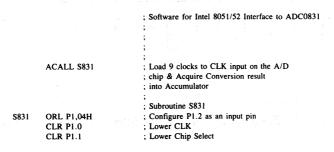

| ADC0831/0832/0834/0838 A/D Converter<br>Interface to Intel 8051 and 8052<br>Microcontrollers                | 11-280   |

| Circuitry – ADC0832, ADC0834 and ADC0838 Devices                                                            | 11 – 280 |

| INTERFACE APPLICATIONS                                                                    | Contents |

|-------------------------------------------------------------------------------------------|----------|

| Timing Diagram-ADC0838 Device                                                             | 11-280   |

| Software-ADC0832, ADC0834 and ADC0838                                                     |          |

| <b>Devices</b>                                                                            | 11-282   |

| Circuitry – ADC0831 Device                                                                | 11 - 284 |

| Timing Diagram-ADC0831 Device                                                             | 11-285   |

| Software - ADC0831 Device                                                                 | 11-285   |

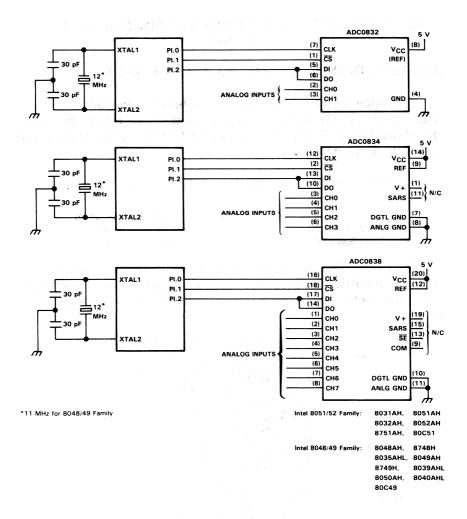

| ADC0831/0832/0834/0838 A/D Converter<br>Interface to Intel 8048 and 8049 Microcontrollers | 11-286   |

| Circuitry – ADC0832, ADC0834 and ADC0838 Devices                                          | 11-286   |

| Timing Diagram-ADC0838 Device                                                             | 11-286   |

| Software – ADC0832, ADC0834 and ADC0838 Devices                                           | 11-287   |

| Circuitry - ADC0831 Device                                                                | 11-288   |

| Timing Diagram-ADC0831 Device                                                             | 11-288   |

| Software - ADC0831 Device                                                                 | 11-289   |

| Section 12<br>Peripheral Drivers                                                          | •        |

| Peripheral Drivers                                                                        | 12-1     |

| INTRODUCTION                                                                              | 12-1     |

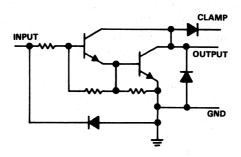

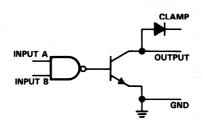

| DEVICE CONSIDERATIONS                                                                     | 12 - 1   |

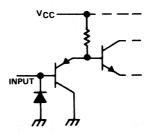

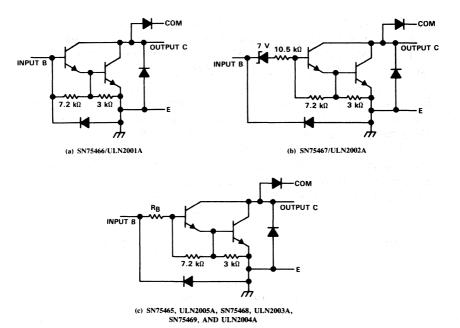

| Basic Configurations                                                                      | 12 - 1   |

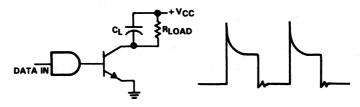

| Typical Requirements                                                                      | 12-2     |

| Power                                                                                     | 12-2     |

| Voltage                                                                                   | 12 - 3   |

| Current                                                                                   | 12 - 3   |

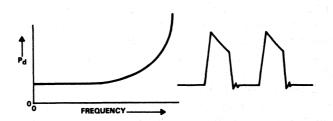

| Speed                                                                                     | 12 - 3   |

| Logic                                                                                     | 12-4     |

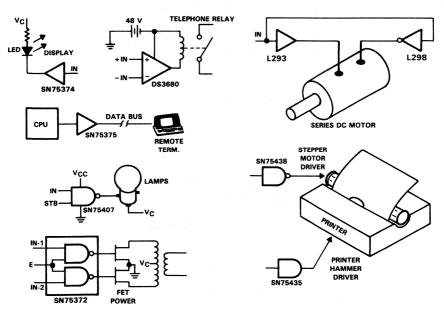

| PERIPHERAL DRIVER DEVICES AND APPLICATIONS                                | 12-5  |

|---------------------------------------------------------------------------|-------|

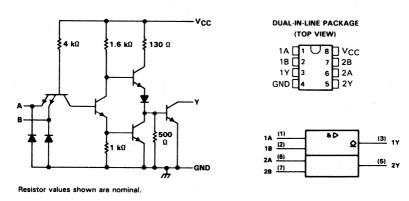

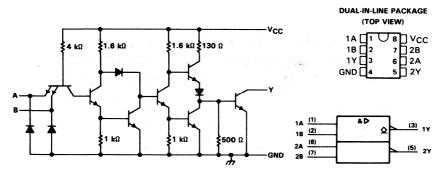

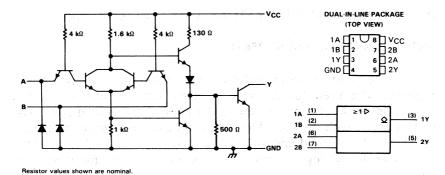

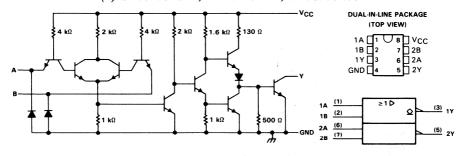

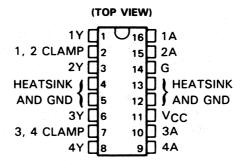

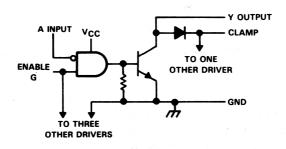

| SN75451, SN75461 and SN75471                                              | 12-5  |

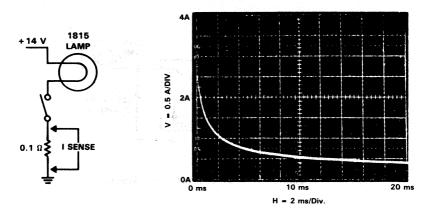

| Driving Tungsten Filament, or Equivalent Incandescent Lamps               | 12-7  |

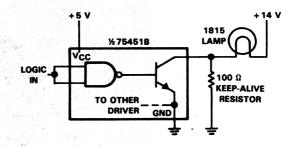

| Using SN75451B to Drive Lamps                                             | 12-7  |

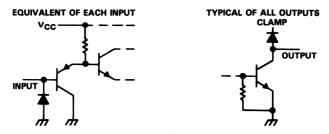

| SN75446 and SN75476 Series                                                | 12-8  |

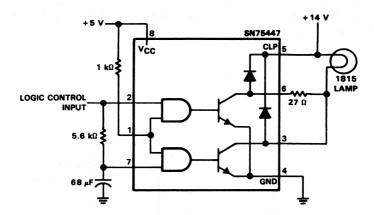

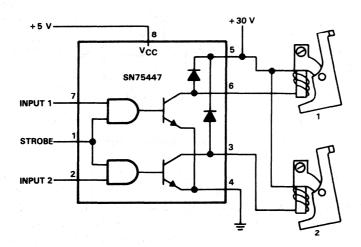

| Incandescent Lamp Driving With SN75447                                    | 12-9  |

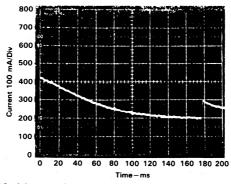

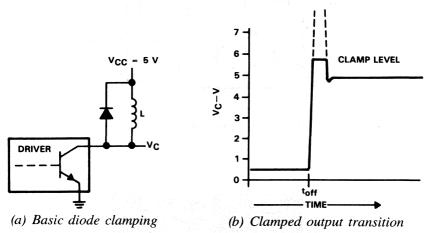

| Relay and Solenoid Drivers                                                | 12-10 |

| SN75447 Print Hammer Driver Application                                   | 12-11 |

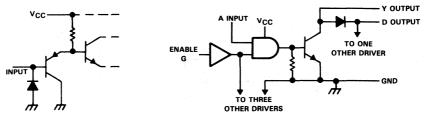

| SN75436, SN75437A and SN75438                                             | 12-12 |

| SN75435 Quad Driver                                                       | 12-13 |

| SN75440 Quad Driver                                                       | 12-15 |

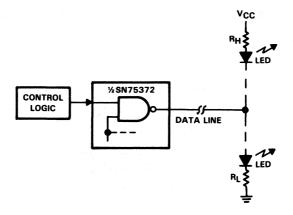

| SN75372 Dual and SN75374 Quad Power FET Drivers                           | 12-17 |

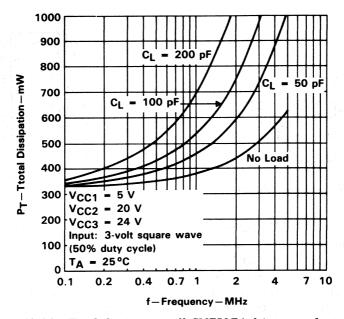

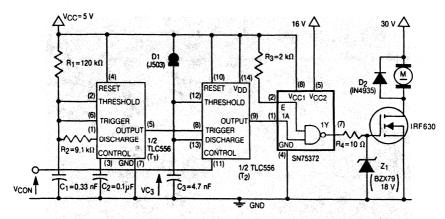

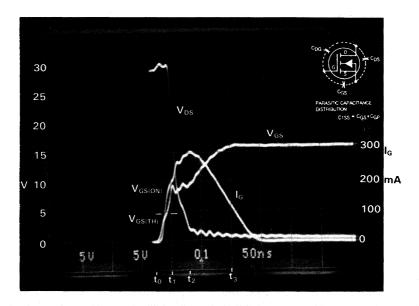

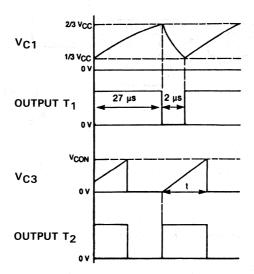

| Driving Power FETs for DC Motor Control with SN75372                      | 12-20 |

| Driving LED Devices with the SN75372                                      | 12-23 |

| DS3680 Quad Telephone Relay Driver                                        | 12-24 |

| DARLINGTON ARRAY DRIVERS                                                  | 12-25 |

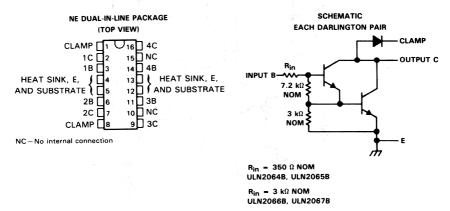

| ULN2064 Series Quad Peripheral Drivers                                    | 12-26 |

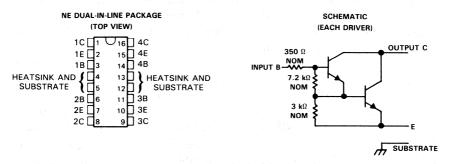

| SN75068/ULN2068 and SN75069/ULN2069 Quad Darlington Switches              | 12-26 |

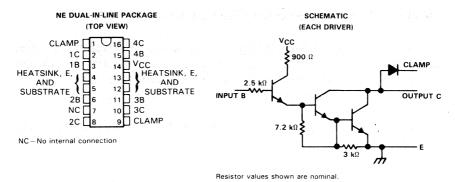

| ULN2074 and ULN2075 Quad Darlington Sink or Source Drivers                | 12-27 |

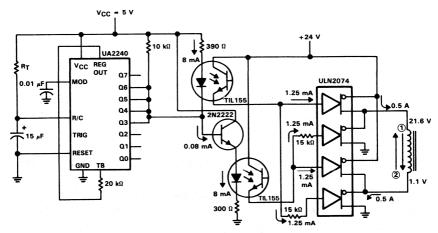

| Driving a Reversible Solenoid Using ULN2074 and ULN2075                   | 12-28 |

| Opto Isolated and Time controlled reversible Solenoid Drive Using ULN2074 | 12-28 |

| SN75465 and ULN2001A Series Seven Darlington                              | 12-20 |

| INTERFACE APPLICATIONS |                                                                                               |            |  |  |

|------------------------|-----------------------------------------------------------------------------------------------|------------|--|--|

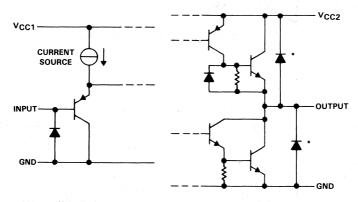

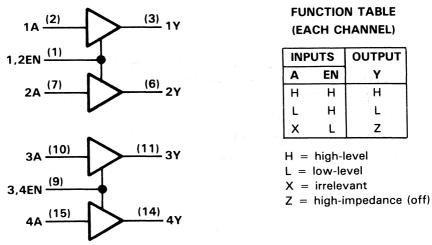

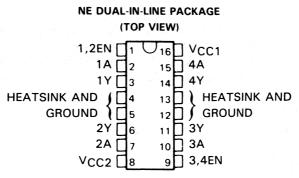

|                        | FULL AND HALF-H DRIVERS                                                                       | 12-31      |  |  |

|                        | L293, L293D, SN754410 and SN754411 Quad<br>Half-H Drivers                                     | 12-31      |  |  |

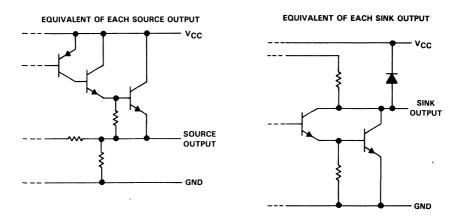

|                        | L298 Dual Full-H Driver                                                                       | 12-33      |  |  |

|                        | L293 and L298 Families Applications                                                           | 12-35      |  |  |

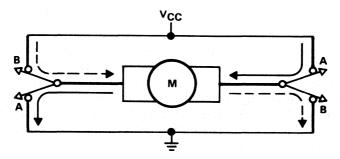

|                        | DC Motor Bridge or "H" Drivers                                                                | 12-35      |  |  |

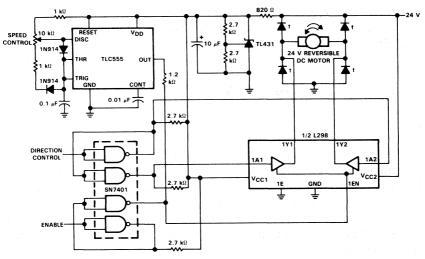

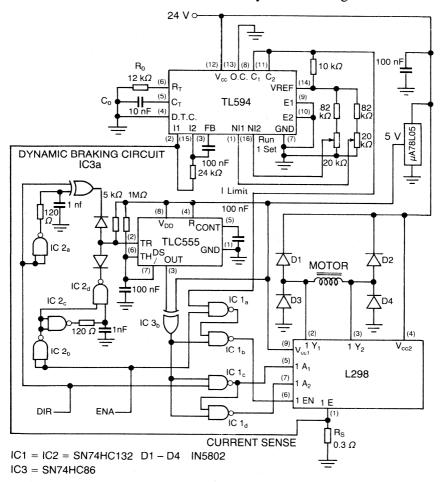

|                        | L298 Speed Controlled Bidirectional DC Motor Driver                                           | 12-35      |  |  |

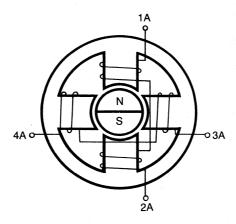

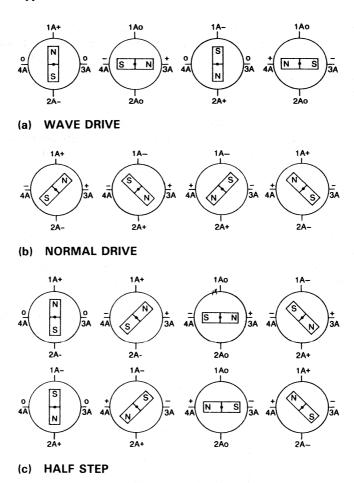

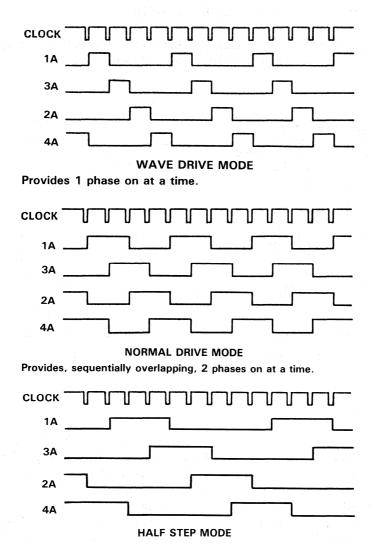

|                        | Stepper Motor Overview and Drives                                                             | 12-36      |  |  |

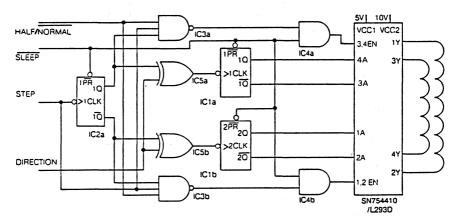

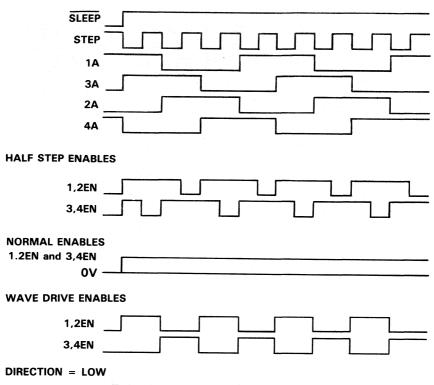

|                        | Stepper Motor Drive Using L293D/SN754410                                                      | 12-40      |  |  |

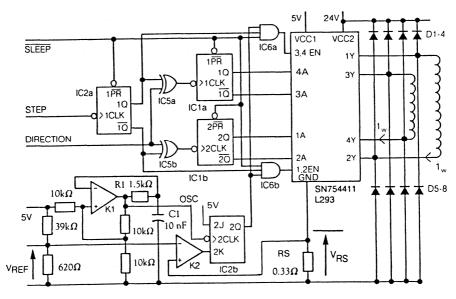

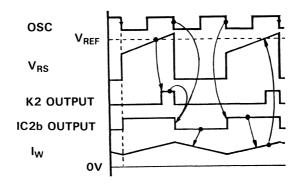

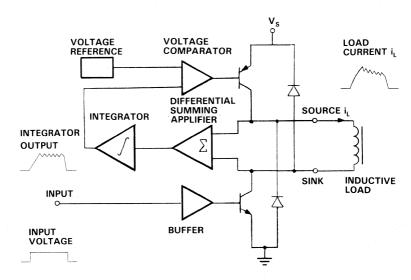

|                        | Wave Drive with Constant Current Control Using L293/SN754411                                  | g<br>12-41 |  |  |

|                        | L298 PWM Servo Motor Control with Dynamic Braking                                             | 12-43      |  |  |

|                        | TLP609 Dual Flux-Regulating Actuator                                                          | 12-45      |  |  |

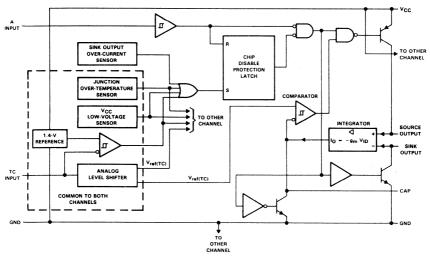

|                        | Principles of Operation                                                                       | 12-46      |  |  |

|                        | TLP609 Operation                                                                              | 12-47      |  |  |

|                        | Dot-Matrix Printhead-Driving with TLP609                                                      | 12-51      |  |  |

|                        | Design Example                                                                                | 12-56      |  |  |

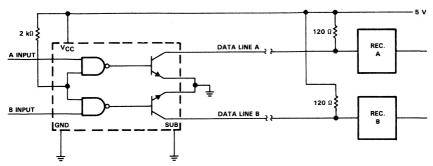

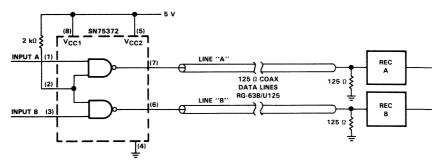

|                        | DRIVING DATA TRANSMISSION LINES (See also Linear and Interface Circuit Applications Volume 2) | 12-57      |  |  |

|                        |                                                                                               |            |  |  |

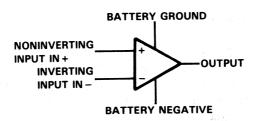

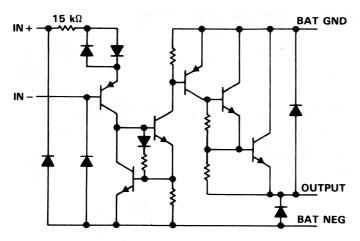

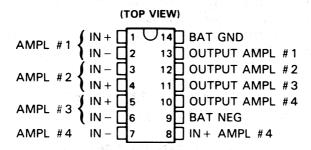

|                        | Section 13 Hall-Effect Devices                                                                |            |  |  |

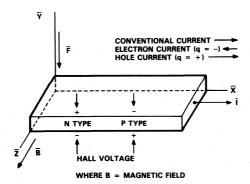

|                        | THE HALL-EFFECT                                                                               | 13-1       |  |  |

|                        | Introduction                                                                                  | 13-1       |  |  |

|                        | The Hell Effect in Silicon                                                                    | 12 1       |  |  |

| Contents |  | LINEAR | AND |

|----------|--|--------|-----|

|          |  |        |     |

|                                        | HALL-EFFECT DEVICES                                               | 13-2  |

|----------------------------------------|-------------------------------------------------------------------|-------|

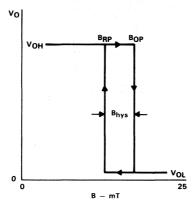

|                                        | Switching Devices                                                 | 13-3  |

|                                        | Latching Devices                                                  | 13-4  |

|                                        | Linear Hall-Effect Devices                                        | 13-4  |

|                                        | Advantages of Hall-Effect Devices                                 | 13-6  |

|                                        | HALL-EFFECT DEVICE SELECTION                                      | 13-6  |

|                                        | HALL-EFFECT APPLICATIONS                                          | 13-7  |

|                                        | TL3103 Linear Hall-Effect Device in Isolated Sencing Applications | 13-8  |

|                                        | Toriod Design                                                     | 13-9  |

|                                        | TL594 Isolated Feedback Power Supply                              | 13-10 |

|                                        | Tachometer and Direction of Rotation Circuit                      | 13-11 |

|                                        | Tachometer Operation                                              | 13-11 |

|                                        | Direction of Rotation Circuit                                     | 13-13 |

|                                        | LED V <sub>CC</sub> Supply Control                                | 13-13 |

|                                        | Angle of Rotation Detector                                        | 13-14 |

|                                        | Hall-Effect Compass                                               | 13-15 |

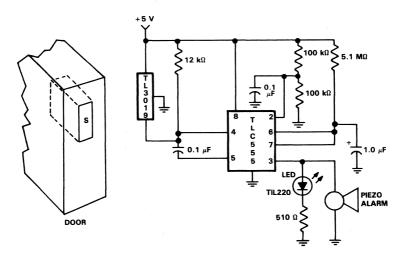

|                                        | Security Door Alarm                                               | 13-16 |

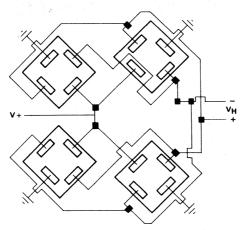

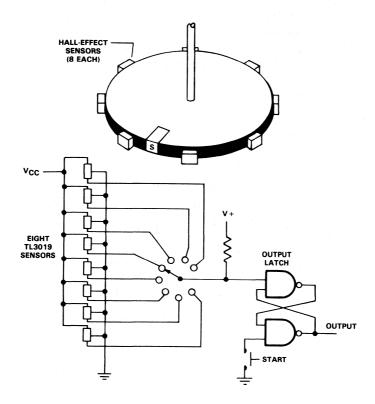

|                                        | Multiple Position Control System                                  | 13-17 |

| ************************************** | Door Open Alarm                                                   | 13-18 |

# **Preface**

This is the third volume in a three-volume series of Linear and Interface Circuit Applications books. To maintain overall continuity in the series, the section numbers in this book follow those in Volume 2. Volume 1 presented information on operational amplifiers, voltage regulators and timers. Volume 2 provides information on display drivers and data transmission line circuits. Volume 3 provides information on data acquisition, peripheral drivers and Hall-effect devices.

The purpose of this series of books is to present linear and interface circuit applications in a manner that will give the reader a basic understanding of the products and provide simple but practical examples for typical applications. Care has been taken to choose illustrations which are of interest, at least by analogy, to a wide class of readers. This material is written for not only the design engineer but also for engineering managers, engineering technicians, systems designers, and marketing or sales people with some technical background. The authors have attempted to avoid lengthy mathematical analyses so that the important points may be clearly emphasized and not obscured by distracting derivations. In cases where a rigorous derivation has been omitted, an attempt has been made to state the results precisely and to emphasize limitations that are practically significant.

To facilitate their use, the sections have been made basically independent. The primary goal of the books is to assist the user in selecting the proper device for a particular application. To accomplish this, key features of devices are presented along with discussions of device or system theory and requirements.

Potential uses of the devices are demonstrated in circuit applications. These applications are not intended to be a how-to for specific circuits but to be examples of how the device might be used to solve your specific design requirements. In each case, a data book or data sheet should be referred to for complete device chracteristics and operating limits. The circuit examples selected for this book have accrued from numerous customer inquiries and related laboratory simulations.

#### LINEAR AND

# Section 11

# **Data Acquisition**

#### INTRODUCTION

This data acquisition section, after a general introduction of basic ideas, will concentrate on single-chip data acquisition devices and give applications information on how they may be interfaced to popular microprocessors. This text will assume that sensors and transducers have already converted physical stimuli into analog electrical signals.

#### TYPICAL SYSTEMS

Data acquisition is the process of transforming analog electrical signals into digital information for: storage, display, processing, further transmission or control. A data acquisition system is an electronic system used to perform this task and comprises sensors, transducers, signal conditioning and sample and hold circuits, analog multiplexers, and analog to digital (A/D) converters. Recovery of a digital signal into analog form is sometimes required. The components, such as digital to analog converters (DAC) and filters, used to perform this function are also covered under the heading of data acquisition.

Data acquisition systems encompass a wide range of applications and implementations. Examples range from simple digital voltmeters, that display an input voltage measured as a numerical output, to large automatic process control systems that incorporate a data acquisition system and a mainframe computer. Data acquisition systems fulfil the need of computing devices of all sizes to retrieve information from the outside world. These

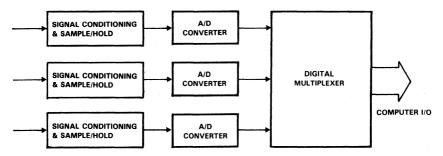

Fig. 11.1 Digital multiplexing of a multi-channel data acquisition system

can then be used to monitor or control processes of many types either locally or remotely.

Typical data acquistion system multi-input configurations are shown in Figs. 11.1 to 11.3. These may be used with any level of computing power, called a host processor in this text, either mainframe, mini, microprocessor or microcomputer, depending on the application.

Flexibility and versatility are features of the digitally multiplexed multichannel system of Fig. 11.1 which has become increasingly feasible with the reducing cost of A/D devices. A/D converters with 3-state outputs and I/O port interfaces make this scheme easy to implement and allows the optimum component choice for each channel. If a serial interface to the digital multiplexer is used, low level analog signals can be digitised at source. This removes problems of interference and allows the possibility of including isolation by, for example, optocouplers. Larger systems can use data reduction, by manipulation of data before transmission, so that the work load of the communication channel is reduced, with only changes and new information being received by the host processor.

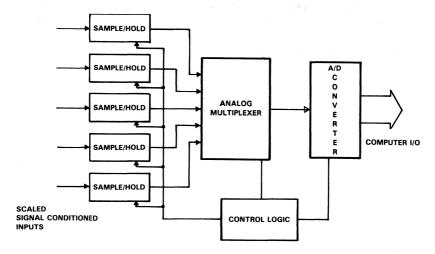

Fig. 11.2 Sample and hold outputs multiplexed to one A/D converter

Multiplexing the outputs of many sample and hold circuits, Fig. 11.2, produces a high speed, multi-channel, one-shot data capture capability. This configuration is useful in test applications where many items of data need to be collected at the same instant, but where there is time for a single

A/D converter to be sequenced through all the sample and hold's outputs. The hold and droop specifications of the sample and hold circuits need to be sufficient for the error performance required.

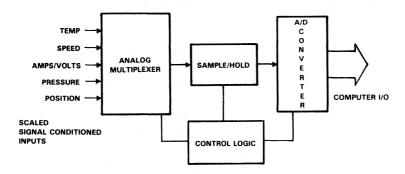

Fig. 11.3 Inputs multiplexed to one sample and hold and A/D converter

Multiplexing the analog signals to the input of one sample and hold circuit and A/D converter, Fig. 11.3, uses the minimum number of components to implement a multi-channel data acquisition system. The overall system is slower, but random input channel access allows the channels with the fastest changing input signal to be converted more frequently. This scheme is most often favoured for single chip data acquisition system implementations, especially those with a switched capacitor A/D converter which have an inherent sample and hold function.

Key parts of the Data Acquisition Systems of Figs. 11.1 to 11.3 include:

Signal Conditioning—This usually preceeds the multiplexer and sample and hold and is used to process the input signal ready for conversion. The conditioning might provide differential inputs, scaling, programmable gain, linear or logarithmic amplification, filtering, isolation, linearisation, etc.

Analog Multiplexer—This, by selecting between several analog input signals, allows the use of only one A/D converter.

Sample and Hold—This acquires and tracks the input signal, ready to sample at the instant required and then hold its output at the sampled value for the duration of the A/D conversion.

Analog-to-Digital Converter (A/D)—This converts an analog input signal into a digital output. A steady input signal, by comparison with a reference, is quantised into discrete levels which are then encoded into a digital form, usually binary. The analog resolution depends on the number of bits in the output code and the size of the reference voltage.

Computer I/O—This describes the A/D Input/Output data and control function. It usually has a serial or parallel 3-state data output and uses a Chip Select, a Write/Read control and an End of Conversion output to implement A/D operation under host processor control. Write is used to start conversion, Read is used to receive output data and these controls may be either signal lines or bits set in A/D control registers. End of Conversion output, when available, can be used in either interrupt or polling schemes with the host processor.

# **Typical Data Acquisition Applications**

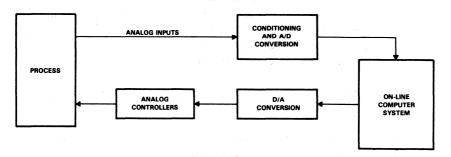

A data acquisition system (DAS) is a self contained subsytem which can communicate with many other systems. On some occasions the DAS is the major part of the system, for example when the system function is data acquisition, as with data logging. The DAS may include a feedback control path, Fig. 11.4, for local process control. On other occasions the DAS is a relatively minor part of another major system and is ancillary to the main function e.g. monitoring a telecoms' line voltage.

Fig. 11.4 A Data acquisition system with a feedback control path

Examples of the broad DAS application areas follow:

Data Logging: Meteorology

**Environment-Structural-Safety**

Water Supply Medical

Aviation

Automatic testing

Process Control &

Refineries

Control Systems: Food and Drink Processing

Manufacturing: Steel to Semiconductors Energy Supply: Electricity, Gas, Oil, Nuclear Automotive: Engine Management, Suspension,

Anti-lock brakes, Anti-slip

Environmental: Heating, Air Conditioning

Marine Mining

Communications:

Telecommunications

Video Graphics Digital Television

Railways

# Data Logging

Data logging involves measuring the analog inputs and translating the results into digital signals which are stored for further processing or analysis.

# Process Control and Control Systems

This is differentiated from data logging by the real time control that is exercised on the basis of the gathered data. The feedback may be either included locally as part of a data acquisition subsytem, which may be the entire system, or globally from a larger central host processor or both.

#### Communications

Communications in a very broad sense can be included as a category of data acquisition, electrical signals are digitised, stored with an emphasis on transmission.

#### BASIC CONCEPTS

#### Signals and Data Acquisition Sampling Systems

Signal characteristics are an important consideration when choosing data acquisition components and sampling rates. Account should be taken of whether the signal being digitised is either dc, a one-shot transient event or a continuous time varying wafeform (i.e. composed of sinusoidal components). In conjunction with these, such parameters as maximum frequency, signal to noise ratio and maximum amplitude also need consideration.

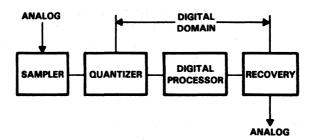

Fig. 11.5 Data acquisition sampling system

A block diagram is shown in Fig. 11.5 of a complete data acquisition process from analog-to-digital conversion through to recovery including digital-to-analog conversion. The signal sampling process and other functions are further discussed below.

#### Sampling Rate and Aliasing

Continuous Time Signals and Nyquist's Criterion

Sampling is the first step in representing a continuous time signal in a discrete time, sampled data or digital signal, form. Sampling is achieved by instantaneously measuring a continuous waveform at regular discrete intervals called the sampling period, the inverse of which is the sampling rate. Ideally sampling should be performed by impulses, infinitesimally narrow pulses of unit area, on bandlimited continuous time input signals. Under these conditions, the Nyquist criterion for sampling rate states that all the information in a signal can be extracted if it is sampled at a frequency,  $f_s$ , greater than twice the highest input frequency. This is called the Nyquist rate.

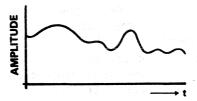

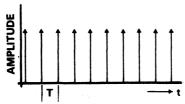

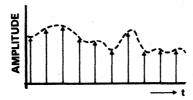

#### Ideal Sampled Frequency Spectrum

(a) Band-limited continuous-time signal

(b) Sampling impulses spaced at sampling period T

(c) Amplitude modulated sampling impulses

Fig. 11.6 Sampling in the time domain

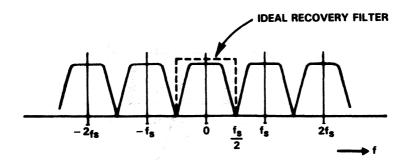

Fig. 11.7 Frequency spectrum of time sampled continuous signals at the Nyquist rate

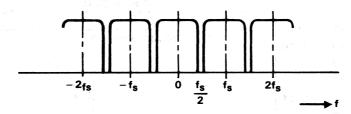

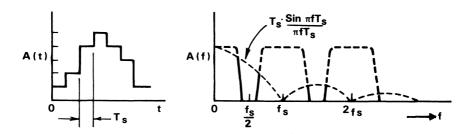

Sampling in the time domain produces an impulse train that is amplitude modulated by the bandlimited input signal, Fig. 11.6. In the frequency domain the frequency spectrum of the sampling process consists of discrete frequencies at multiples of the sampling rate with double sidebands produced by the amplitude modulation, Fig. 11.7.

This describes the ideal process and shows that sampling adds new frequency components to the original frequency spectrum. Ideal recovery of the original signal would require an ideal low pass filter, of half Nyquist rate bandwith, to remove all but the original signal spectrum, Fig. 11.7.

#### Aliasing

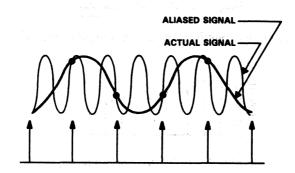

Fig. 11.8 Aliasing in the time domain due to sampling below the Nyquist rate

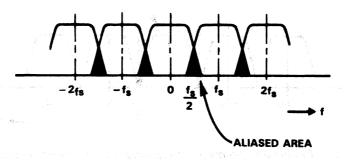

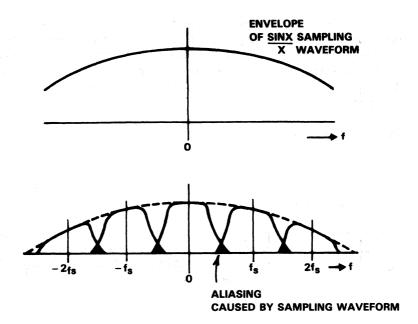

Fig. 11.9 Aliasing in the frequency domain

If sampling is lower than the Nyquist rate then the separation between the double sidebands of Fig. 11.7 disappear and they overlap. Higher frequency components fold back into the frequency range of the input signal bandwith and take on the identity of lower frequencies. This effect is called Aliasing, Figs. 11.8 and 11.9. This form of distortion is usually impossible to remove once it has occurred.

#### **Practical Constraints**

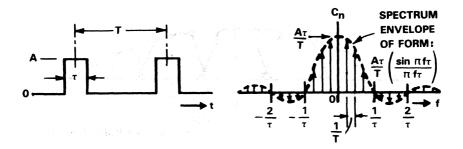

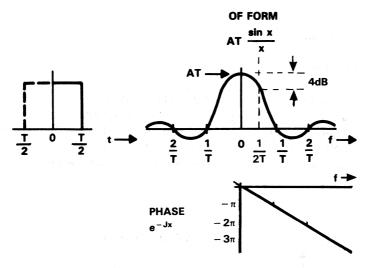

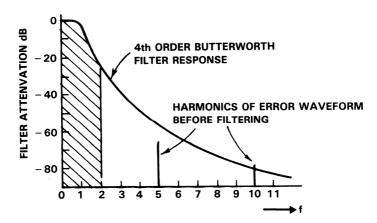

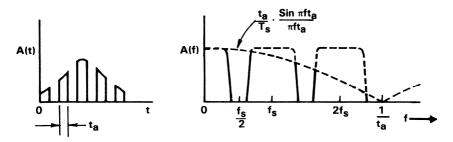

Fig. 11.10 Rectangular pulse train with frequency spectrum

Practically, the sampling waveform will not be an impulse but a pulse of finite width. The wider the sampling pulses become the greater the effect on the sampled signals spectrum. The sampling pulses, Fig. 11.10, have a sinx/x frequency spectrum which causes an extension in effective input signal bandwidth and high frequency attenuation after sampling, Fig. 11.11. This can aggravate problems with aliasing and is avoided by keeping sampling pulse widths small in comparison with the sampling period. From the expression for frequency domain amplitude response, of Fig. 11.10. it can be shown that sampling pulses  $\tau$  of one-fifth the sampling period T give less than 0.1 dB attenuation at a frequency of 0.4 fs. There are also practical constraints which limit the roll-off rates of real filters that band-limit the input frequency.

The constraints described above will increase the input bandwidth and modify the sampled input frequency spectrum. To account for this the sampling rate should be raised from the minimum given by the Nyquist criterion. Increasing the sample rates from the Nyquist minimum, to 10 samples per input cycle at maximum frequency, significantly increases the accuracy of a recovered signal. Without the use of reconstruction filters, the accuracy improves from approximately 30% to over 90%.

Fig. 11.11 Finite Sampling Pulse Width Effect on Sampled Frequency Spectrum of Fig. 11.7

# Sampling Transient Signals

Transient or one-shot input signals demand a different approach to sampling than continuous signals. Sample rate has to be determined from the slew rate of the transient and resolution requirements. Pre-knowledge of the signal characteristics will ease this decision. For example, information that a transient has passed through a bandpass filter will define its maximum slew rate. Specified interpolation requirements can also be used to determine sampling rates.

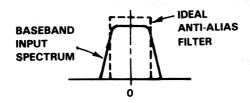

# **Anti-Aliasing Filter**

Noise and out-of-band input signals can be prevented from folding over into the signal bandwidth of interest by employing some form of presampling filter, most often called an anti-aliasing filter. An ideal filter response shape would be the "brickwall" filter shown in Fig. 11.12, which stops signal sidebands overlapping. Such filters are impossible to construct and complex filters that attempt the task introduce phase and amplitude

distortion of their own. The solution lies in a compromise between sample rate and anti-aliasing filter complexity.

#### (a) Baseband spectrum

#### (b) Sampled spectrum

Fig. 11.12 Removal of aliasing components with pre-sample or "anti-aliasing" filter

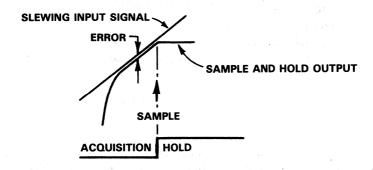

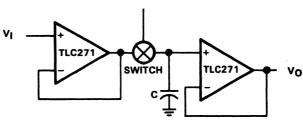

# Acquisition

Fig. 11.13 Acquisition action of a sample and hold\*circuit

Acquisition is a term that applies to sample and hold circuits including those incorporated into A/D converters and recognises that before a signal

can be sampled it has to be acquired. These circuits, prior to the sampling instant, charge a capacitor to the input signal level and then track it within an acceptable error specification Fig. 11.13.

#### A/D Conversion

#### **Ouantisation**

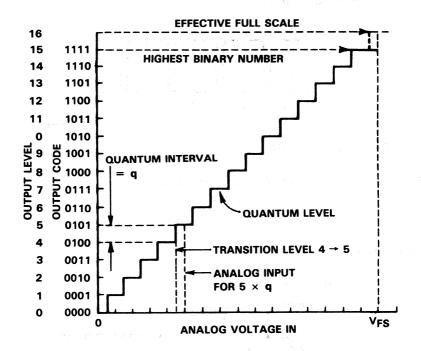

Fig. 11.14 Transfer Funtion for 4-Bit Binary Quantiser

When a continuous signal is represented by a binary sequence of some fixed length 'n', it limits the number of output signal levels that can be defined to 2<sup>n</sup>. Each level is called a quantum and quantisation is the process of representing the input signal by one of these levels. Fig. 11.14 shows how each output quantum level corresponds to a range of input values, and the typical stair-case transfer characteristic of an A/D converter.

32,768 65.536

| n | Levels | n  | Levels |

|---|--------|----|--------|

| 1 | 2      | 9  | 512    |

| 2 | 4      | 10 | 1,024  |

| 3 | 8      | 11 | 2,048  |

| 4 | 16     | 12 | 4,096  |

| 5 | 32     | 13 | 8,192  |

| 6 | 64     | 14 | 16.384 |

Table 11.1 Number of quantisation levels or resolution per binary 'n' bits

Table 11.1 shows the number of quantisation levels versus number of bits 'n'.

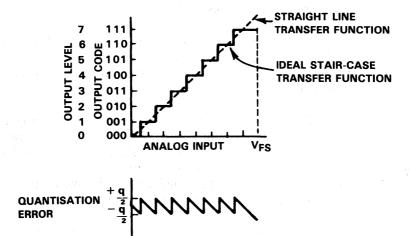

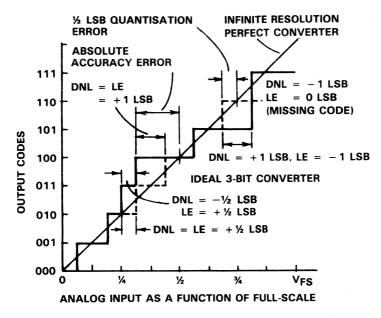

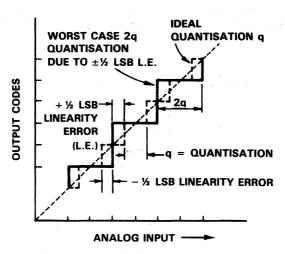

Subtracting a straight line transfer function, which represents an A/D with infinite resolution, from an ideal stair-case A/D transfer function of n-bit resolution, shows the theoretical minimum quantisation error of value  $\pm$  1/2 LSB (Least Significant Bit), or  $\pm$  q/2 where q is one quantum interval. A 3-bit example is shown in Fig. 11.15.

Fig. 11.15 A/D quantisation error, 3-bit example

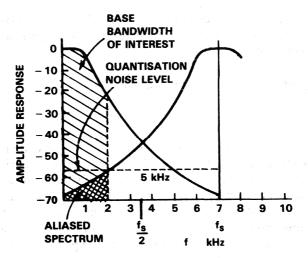

#### Quantisation noise

Quantisation effectively adds noise to an A/D converter's output signal, in a similar way to many other signal conditioning functions such as amplification. This quantisation noise is usually considered as as uniformly random sequence that has a rms value =  $q/\sqrt{12}$  where q is the value of the quantum level. The differential-nonlinearity of practical A/D converters can increase this noise level.

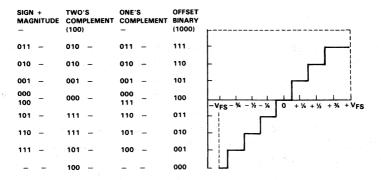

#### Encoding

To complete an A/D conversion process discrete quantised levels, which may be identified as a position on a multi-tap potential divider, have to be translated into some form of digital output code. Some A/D converter architectures internally produce a binary code as part of the quantisation process, successive approximation for example, however the output code may be required in offset binary, 2's complement, BCD or some other format that will need encoding.

#### Resolution

A/D converter resolution is the weight assigned to the least-significant bit (LSB) and is inherent in the output code represented by a number of binary bits 'n'. The weight then equals the full scale reference value divided by 2<sup>n</sup>.

# Dynamic Range and Signal to Noise Ratio

Dynamic range is defined as the range between the noise floor and maximum amplitude of a signal. For an A/D converter this extends from the effective quantisation noise, determined by the number of bits and error performance of a specific device, to the value of reference voltage.

The result of dividing a signal's amplitude, which may be maximum amplitude, by its noise voltage is called the signal to noise ratio. The ratio of root-mean-square (rms) maximum amplitude sinewave input signal to ideal quantisation rms noise, for an A/D converter of 'n' bits, is equal to: S/N = 6.02n + 1.76 dB. If a signal to noise ratio is known an effective value of bits 'n' for an A/D can be determined from this expression.

Dynamic range is a factor when deciding upon the required number of A/D converter bits for a particular application. Using many more bits than is required will result in digitising input noise. An optimum choice

occurs when the noise of the A/D converter quantisation equals that of the incoming signal.

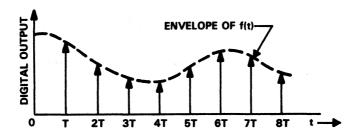

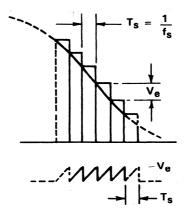

#### Signal recovery

Digital-to-Analog converters are used to produce an analog output from a digital signal processing system. Recovering a continuous time signal from a sample data signal is achieved by a process of interpolation between sample amplitudes in the time domain, Fig. 11.16. This process is equivalent in the frequency domain to using an ideal filter to remove the extra unwanted signals introduced by sampling (see earlier Fig. 11.7).

Fig. 11.16 Ideal amplitude modulated sample pulse train from DAC.

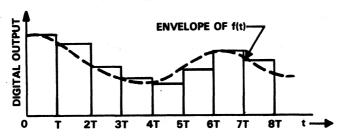

Fig. 11.17 DAC "zero order hold" recovery

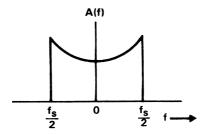

Output impulses of very short duration, Fig. 11.16, do not contain significant power and so after interpolation a very low output amplitude would be obtained. To overcome this, the output of a DAC usually comprises sample-period duration pulses of an amplitude depending on input code. Fig. 11.17 shows the characteristic step interpolator output which has the form of the so-called 'zero-order hold'. Its sinx/x function frequency spectrum and phase characteristic are shown in Fig. 11.18.

Fig. 11.18 Sinx/x frequency spectrum and phase charactersistics

The frequency spectrum of Fig. 11.18 performs a filtering action on the DAC output signal with the first zero in the frequency spectrum occuring at the sampling frequency. If sampling is at the Nyquist rate an amplitude reduction of 4 dB at the maximum input frequency will result. This can be compensated by filtering either in the digital or analog domain. The digital approach will more easily achieve high accuracy. If sampling is very much greater (100:1) than the Nyquist rate, it will allow the use of a simpler post-DAC reconstruction or interpolation filter.

# DATA ACQUISITION TERMINOLOGY

#### Introduction

Terminology referring to data acquisition component parameters and performance, that commonly appear in data sheets and applications information, is described below. It should be noted that on many occasions, there are subtle differences in the meaning of terms when they describe parameters of both analog-to-digital (A/D) and digital-to-analog (DAC) converters. This arises because both have their performance measured and specified with respect to the analog domain.

A particular digital code input to a DAC produces a discrete analog output whereas a range of analog values input to an A/D determine a digital output code. For example: Quantisation, referring to an A/D, describes the input analog range for a particular output code but, for a DAC, describes the ideal difference in analog output between adjacent input codes. A DAC analog output, for a given code, has a discrete value modified only by error specifications.

## Nominal Midstep and Step values

Error terms in general are expressed as deviations from an ideal, or theoretical value, usually in fractions of a least-significant-bit (LSB), but % of full-scale and ppm are sometimes used. For an A/D the nominal midstep value is the error free value corresponding to a particular code which lies on a line between zero and full-scale. Similarly for a DAC an error free discrete analog output for a particular code is called the nominal step value.

## **Absolute Accuracy**

Absolute accuracy defines data acquisition component measurements that are made with voltage sources and measuring instruments traceable to internationally accepted standards.

## **Absolute Accuracy Error or Total Error**

Absolute accuracy error, or total error, of a DAC for a given digital input code, is the difference between the actual step in analog output and the nominal step value.

A/D converter absolute accuracy error, or total error, is the maximum difference between actual input values and the nominal midstep value within any step to produce a given code. Absolute accuracy error includes contributions from offset error, gain error, linearity error and inherent quantisation error.

## **Relative Accuracy Error**

Relative accuracy error is the deviation in analog value from its ideal value relative to the full-scale-range (FSR). This is expressed either as a fraction of an LSB, % FSR or ppm.

#### **Quantisation Error**

Quantisation Error is the inherent error of a converter due to the finite resolution defined by the length of an equivalent digital binary output code, Fig. 11.19.

#### Code Width

For an A/D converter, code width is the range of analog input values over which the same output code will occur. An ideal code width is 1 LSB, that is FSR/2<sup>n</sup> where n is the number of bits for a binary output code, actual code widths vary due to linearity errors.

## Linearity Error (LE) or Integral Nonlinearity (INL)

Linearity error or integral nonlinearity is the maximum difference in analog value at a transition between any two adjacent steps from its ideal value. The ideal value can be determined from either a best straight line fit, without adjustment of full-scale or offset error, or a line passing through the end points of an ideal transfer characteristic, which implies adjustment of full-scale and offset errors to zero, see Fig. 11.19.

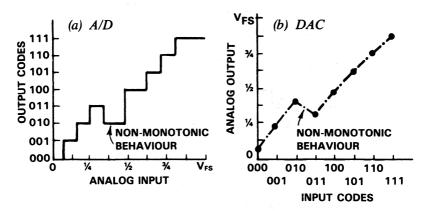

## Differential Nonlinearity (DNL)

Differential nonlinearity for a DAC is the difference in analog output value for adjacent codes minus 1 LSB, this can have a positive or negative value. For a DAC, if DNL is more negative than -1 LSB a non-monotonic response will result where the analog output decreases for an increasing input code value.

Differential nonlinearity for an A/D is the difference between actual code width and an ideal code width of 1 LSB, see Fig. 11.19. Corresponding to the non-monotonic behaviour of a DAC with DNL more negative than -1 LSB, an A/D will exhibit missing codes in its output if DNL equals -1 LSB. A linearity error specification of  $\pm \frac{1}{2}$  LSB infers a DNL of not greater than -1 LSB.

Some manufacturers quote A/D DNL as the actual difference in adjacent code midpoints minus 1 LSB, instead of actual code width minus 1 LSB. The missing code condition remains the same, at DNL equal to -1 LSB, but other values of DNL will apparently be different between the two specification methods.

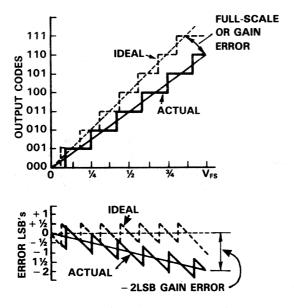

(a) 3-bit A/D converter ideal and hypothetical error transfer characteristics

(b) Example error curve (actual-perfect transfer characteristic)

NOTE: EXAMPLES OF THE FOLLOWING ERRORS ARE SHOWN:

DIFFERENTIAL NONLINEARITY (DNL)

LINEARITY ERROR (LE) (INTEGRAL NONLINEARITY)

ABSOLUTE ACCURACY ERROR

QUANTISATION ERROR

TOTAL UNADJUSTED ERROR (TUE)

(WITHOUT ZERO OR FULL-SCALE ERRORS INCLUDED)

Fig. 11.19 Examples of nonlinearity errors

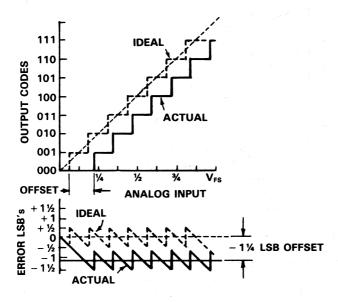

#### **Zero-Scale Error or Offset Error**

Fig. 11.20 3-bit A/D zero or offset error example

Zero-scale error is the difference between the actual and nominal step or midstep value at the specified zero scale point for both unipolar and bipolar devices. Devices are called unipolar when they allow an input voltage range from either  $+V_{FS}$  or  $-V_{FS}$  to zero, or bipolar when they allow an input voltage range of  $-V_{FS}$  to  $+V_{FS}$ .

Offset error, for an A/D, is a deviation of equal value from ideal transition voltages for all codes, as shown in Fig. 11.20. Offset error is specified at the first LSB transition, as zero error, because other errors are not significant at this transition. For a DAC offset is a deviation of equal value to the nominal step value. The term zero-scale error is usually applied to converters without provision for external adjustment of offset error.

#### **Full-Scale or Gain Error**

Full-scale error is the difference between the actual and nomimal step or midstep values at full-scale. Gain error, applies when offset error has been adjusted to zero and, appears as a change in the slope of a converter

Fig. 11.21 3-bit A/D full-scale or gain error example

transfer function by effecting each code in equal ratio, see Fig. 11.21. The term full-scale error is usually applied to converters without provision for external adjustment of offset and gain error.

## **Adjusted Error**

Adjusted error refers to linearity errors that converters, with the provision of exernal gain and offset adjustment, have after these errors are reduced to zero.

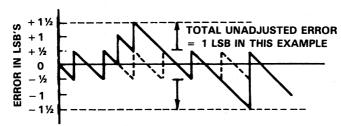

## Total Unadjusted Error (TUE)

Total unadjusted error, applies to converters without the provision for external adjustment of errors and is the sum of offset, gain and linearity errors at any point over the full-scale range. Although the error curve of Fig. 11.19 (b) shows only linearity errors, it illustrates a total unadjusted error boundary, ranging from the quantisation error. A complete error curve would include the offset and gain errors of Fig. 11.20 and 11.21 respectively.

#### **Monotonicity**

Fig. 11.22 Non-monotonic behaviour of an A/D and a DAC

Monotonicity is a converter transfer function behaviour that ensures a consistent increase or decrease in the analog output of a DAC or digital output of an A/D in response to a consistent increase or decrease in the digital or analog input respectively. Fig. 11.22 illustrates non-monotonic conversion.

## **Missing Codes**

Missing codes are intermediate digital output codes of an A/D that, with a changing analog input, fail to occur and cause multiple code output steps, see Fig. 11.19. Differential nonlinearity of -1 LSB is synonymous with missing codes.

## **Acquisition Time**

Acquisition time refers to sample and hold circuits, and A/D converters that include this function, and defines the time needed to acquire a signal to within a specified accuracy.

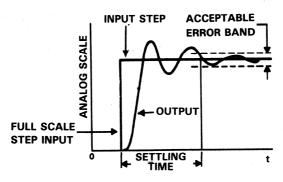

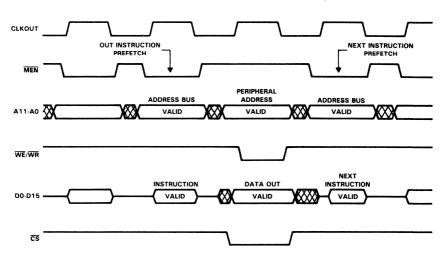

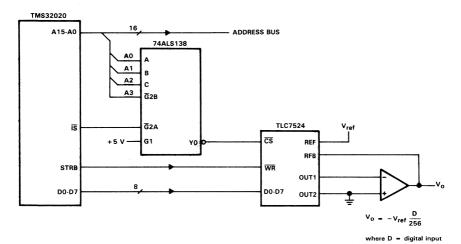

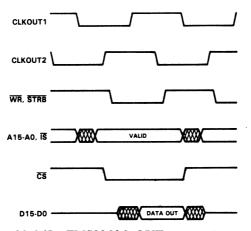

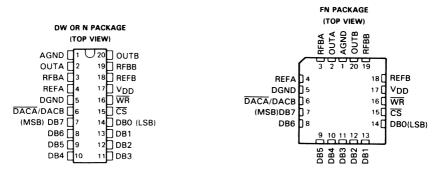

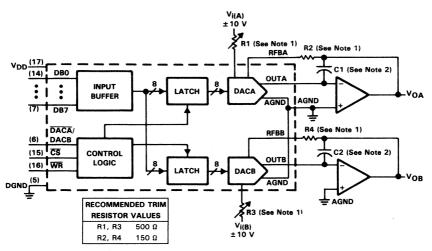

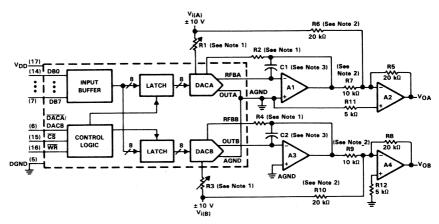

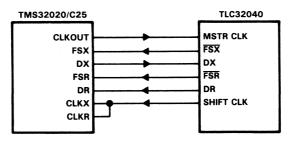

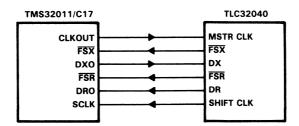

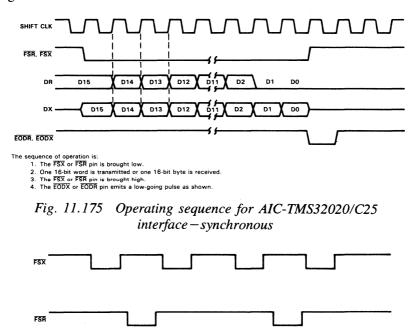

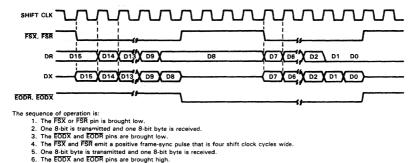

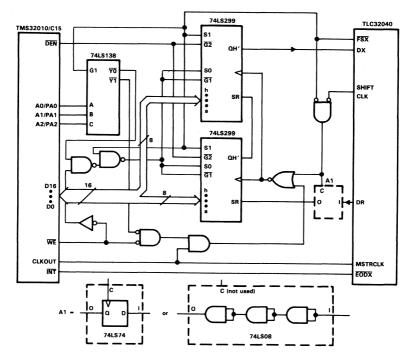

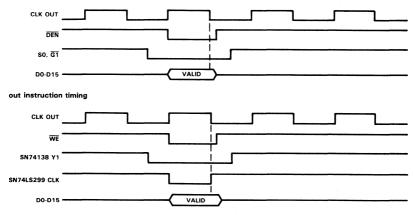

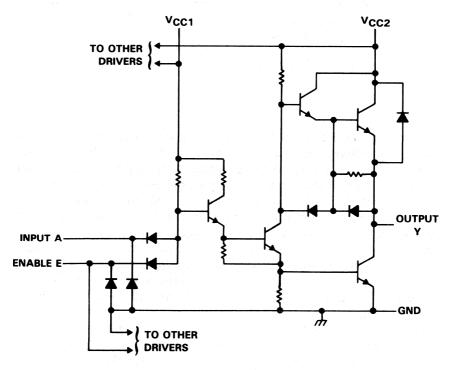

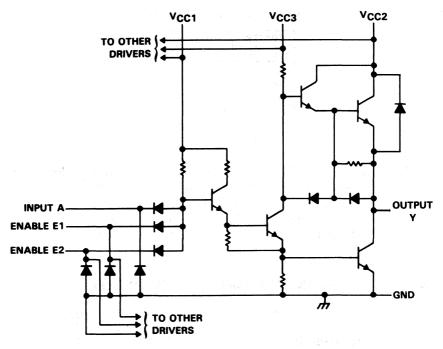

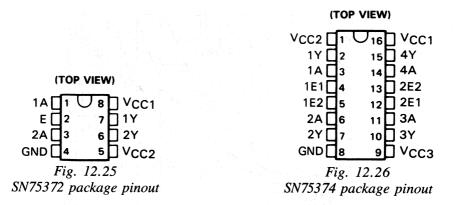

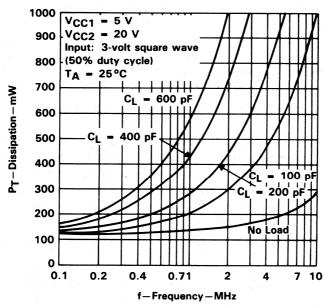

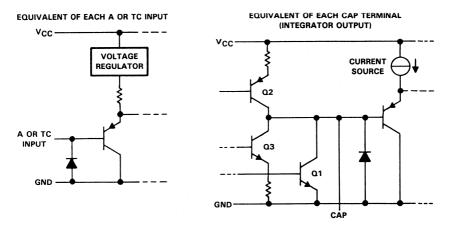

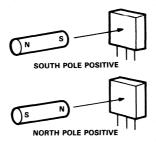

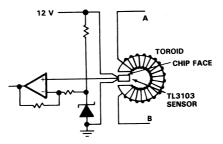

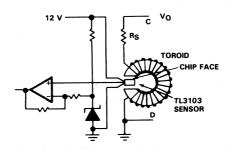

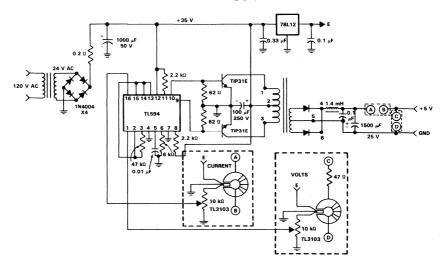

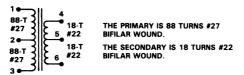

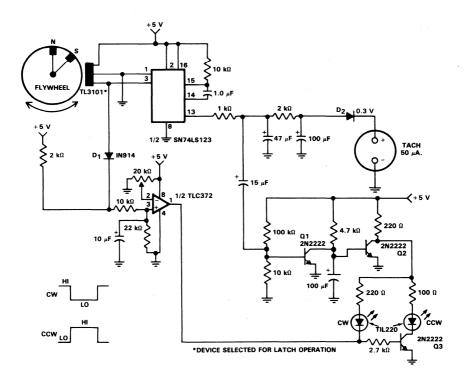

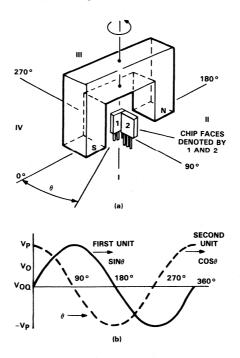

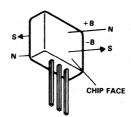

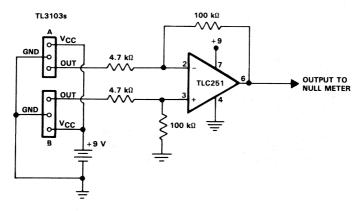

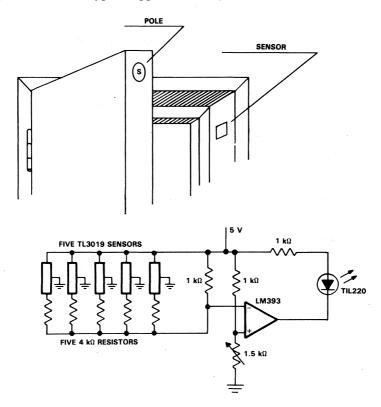

# **Aperture Time**